Intel D845GLAD Product Guide - Page 67

Interrupts, Table 35.

|

UPC - 735858153386

View all Intel D845GLAD manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 67 highlights

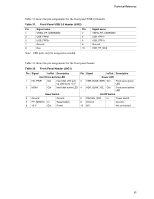

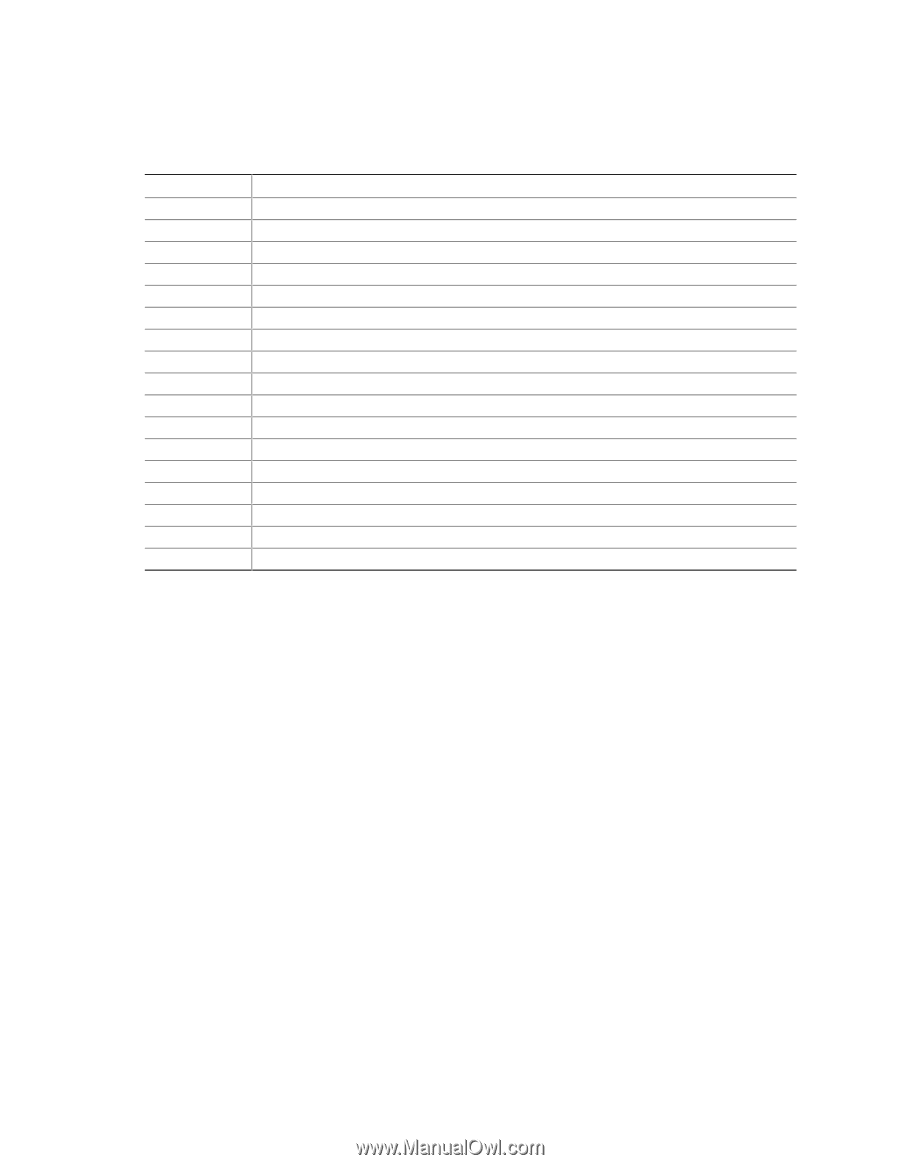

Interrupts Table 35. Interrupts IRQ System Resource NMI I/O channel check 0 Reserved, interval timer 1 Reserved, keyboard buffer full 2 Reserved, cascade interrupt from slave PIC 3 COM2* 4 COM1* 5 LPT2 (Plug & Play option) / ** 6 Diskette drive controller 7 LPT1* 8 Real time clock 9 ** 10 ** 11 ** 12 Onboard mouse port (if present, else user available) 13 Reserved, math coprocessor 14 Primary IDE (if present, else user available) 15 Secondary IDE (if present, else user available) * Default, but can be changed to another IRQ. ** Dynamically allocated for all PCI/AGP devices and slots. Technical Reference 67

Technical Reference

67

Interrupts

Table 35.

Interrupts

IRQ

System Resource

NMI

I/O channel check

0

Reserved, interval timer

1

Reserved, keyboard buffer full

2

Reserved, cascade interrupt from slave PIC

3

COM2*

4

COM1*

5

LPT2 (Plug & Play option) / **

6

Diskette drive controller

7

LPT1*

8

Real time clock

9

**

10

**

11

**

12

Onboard mouse port (if present, else user available)

13

Reserved, math coprocessor

14

Primary IDE (if present, else user available)

15

Secondary IDE (if present, else user available)

*

Default, but can be changed to another IRQ.

** Dynamically allocated for all PCI/AGP devices and slots.