Intel DG33TL Product Specification - Page 35

Fan Headers, 13.2.3, LAN Wake Capabilities, CAUTION - cpu fan

|

View all Intel DG33TL manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 35 highlights

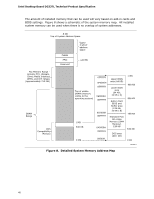

Product Description 1.13.2.2 Fan Headers The function/operation of the fan headers is as follows: • The fans are on when the board is in the S0 state. • The fans are off when the board is off or in the S3, S4, or S5 state. • The CPU fan header is wired to a fan tachometer input and the Front and Rear fan headers share the tachometer input of the hardware monitoring and fan control device. All fan headers support closed-loop fan control that can adjust the fan speed or switch the fan on or off as needed. • All fan headers have a +12 V DC connection. For information about The locations of the fan headers and thermal sensors The signal names of the processor fan header The signal names of the chassis fan headers Refer to Figure 6, page 30 Table 18, page 47 Table 17, page 47 1.13.2.3 LAN Wake Capabilities CAUTION For LAN wake capabilities, the +5 V standby line from the power supply must be capable of providing adequate +5 V standby current. Failure to provide adequate standby current when implementing LAN wake capabilities can damage the power supply. LAN wake capabilities enable remote wake-up of the computer through a network. The LAN subsystem PCI bus network adapter monitors network traffic at the Media Independent Interface. Upon detecting a Magic Packet* frame, the LAN subsystem asserts a wake-up signal that powers up the computer. Depending on the LAN implementation, the board supports LAN wake capabilities with ACPI in the following ways: • The PCI Express WAKE# signal • The PCI bus PME# signal for PCI 2.3 compliant LAN designs ⎯ By Ping ⎯ Magic Packet • The onboard LAN subsystem • Wake from CIR 35