Asus P5P800 SE Motherboard Installation Guide - Page 82

Chipset

|

View all Asus P5P800 SE manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 82 highlights

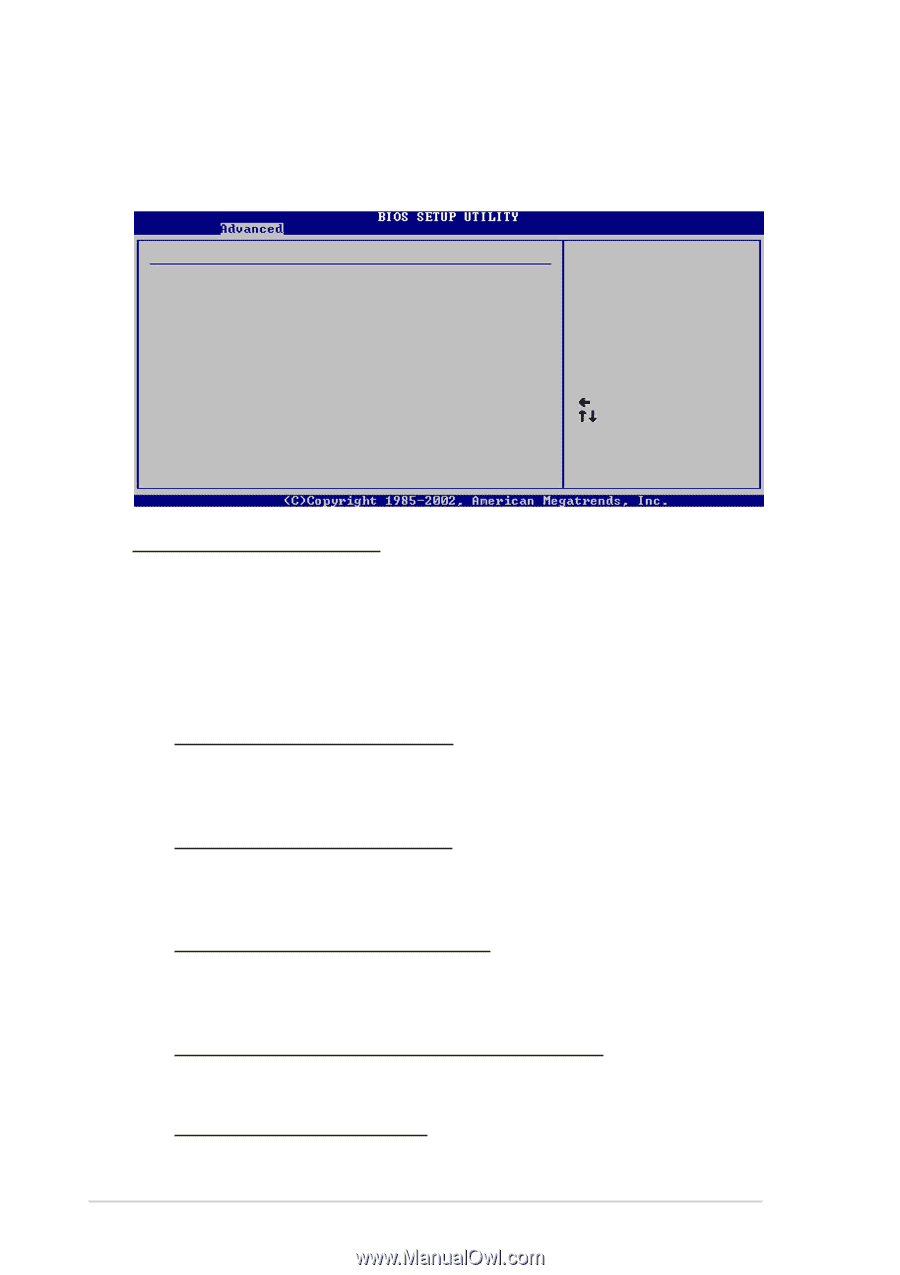

4.4.3 Chipset Le menu chipset vous permet de modifier les paramètres avancés du chipset. Choisissez un élément et pressez pour afficher le sous-menu. Advanced Chipset Settings WARNING: Setting wrong values in the sections below may cause the system to malfunction. Configure DRAM Timing by SPD Memory Acceleration Mode DRAM Idle Timer DRAM Refresh Rate [Enabled] [Auto] [Auto] [Auto] Graphic Adapter Priority Graphics Aperture Size Spread Spectrum [AGP/PCI] [ 64MB] [Enabled] MPS Revision [1.1] Select Screen Select Item +- Change Option F1 General Help F10 Save and Exit ESC Exit Advanced Chipset Settings Configure DRAM Timing by SPD [Enabled] Lorsque cet élément est activé, les paramètres de timing de DRAM sont réglés en fonction du SPD de la DRAM (Serial Presence Detect). Désactivé, vous pouvez régler les paramètres de timings DRAM à la main via les sousélements. Les sous-éléments suivants apparaissent lorsque cet élément est passé sur Disabled. Options de configuration: [Disabled] [Enabled] DRAM CAS# Latency [2.5 Clocks] Contrôle la latence entre la commande de lecture SDRAM et le temps auquel la donnée devient effectivement disponible. Options de configuration: [2.0 Clocks] [2.5 Clocks] [3.0 Clocks] DRAM RAS# Precharge [4 Clocks] Contrôle les périodes dʼinactivité après avoir envoyé une commande precharge à la DDR SDRAM. Options de configuration: [4 Clocks] [3 Clocks] [2 Clocks] DRAM RAS# to CAS# Delay [4 Clocks] Contrôle la latence entre la commande active de la DDR SDRAM et la commande lecture/écriture. Options de configuration: [4 Clocks] [3 Clocks] [2 Clocks] DRAM RAS# Activate to Precharge Delay [8 Clocks] Règle le timing RAS Activate sur Precharge timing. Options de configuration: [8 Clocks] [7 Clocks] [6 Clocks] [5 Clocks] DRAM Burst Length [8 Clocks] Règle la fonction Burst Length de DRAM Options de configuration: [4 Clocks] [8 Clocks] 4-22 Chapitre 4: Le BIOS