Foxconn A76ML-K English Manual. - Page 35

CPU Configuration - 3 0 specification

|

View all Foxconn A76ML-K manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 35 highlights

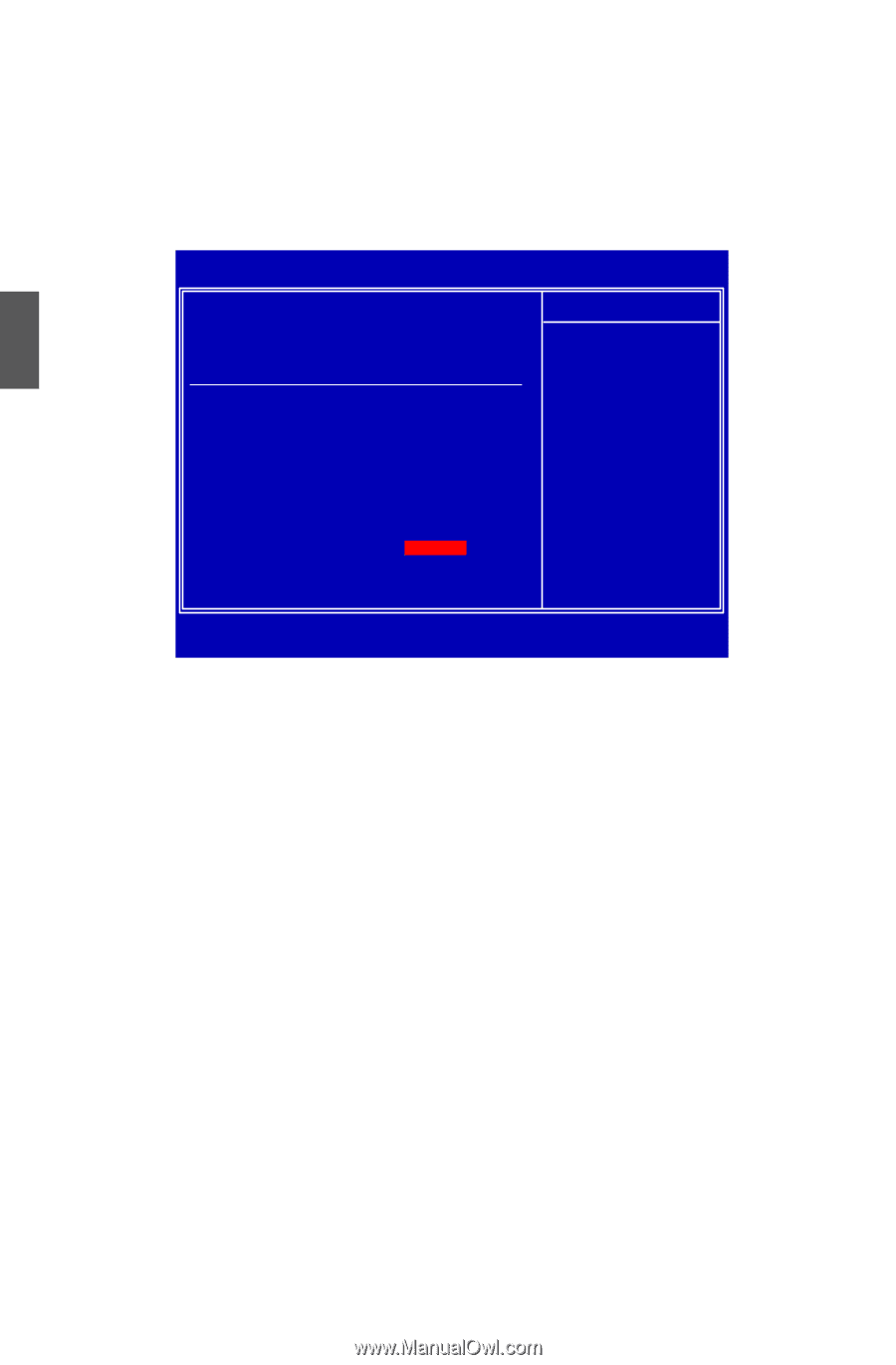

3 mented from +30mV to +360mV. ► HT/SB Voltage Control This option is used to change the HT/SB voltage in a step of 30mV. The voltage can be incremented from +30mV to +360mV. CPU Configuration CMOS Setup Utility - Copyright (C) 1985-2008, American Megatrends, Inc. CPU Configuration CPU Configuration Help Item Module Version : 13.37 AGESA Version : 3.1.9.1 Enable/disable the Physical Count : 1 generation of ACPI Logical Count : 4 _PPC, _PSS, and _PCT objects . AMD Phenom(tm) 9750 Qund-Core Processor Revision : B3 Cache L1 : 512KB Cache L2 : 2048KB Cache L3 : 2MB Current CPU Speed : 2400MHz, Current FSB Multiplier : 12x Able to Change Freq. : Yes uCode Patch Level : 0x1000083 Cool 'N' Quiet [Enabled] C1E Support [Disabled] CPU-NB HT Link Speed [Auto] NCHT Incoming Link Width [Auto] Move Enter:Select +/-/:Value F10:Save ESC:Exit F1:General Help F9:Optimized Defaults This menu shows most of the CPU specifications. ► Cool 'N' Quiet (Appears only when CPU supports) This option helps lowering down the CPU frequency and voltage when system is idling. When the CPU speed is slowing down, the temperature will drop as well. ► C1E Support (Appears only when CPU supports) C1E represents Enhanced HALT State. It is a feature which CPU uses to reduce power consumption when in halt state. C1E drops the CPU's multiplier and voltage to lower levels when a HLT (halt) command is issued. This item is used to enable/disable the C1E support. ► CPU-NB HT Link Speed HT stands for HyperTransport bus. The CPUNB HT Speed option controls the physical speed of the CPU to Northbridge HT link using multipliers ranging 1x to 13x. The physical speed of the link is determined by multiplying the CPU clock with the CPUNB HT Speed setting. ► NCHT Incoming Link Width / NCHT Outgoing Link Width The coherency refers to the caching of memory, and the HT links between processors are coherent HT links as the HT protocol includes messages for managing the cache protocol. Other (non processor-processor) HT links are Non-Coherent HT links, as they do not have memory cache. The HyperTransport link width and frequency are initialized between the adjacent coherent and/or noncoherent HyperTransport technology devices during the reset sequence. It is highly recommended to set to [Auto] for overall performance. 28