Gigabyte GA-P67A-UD7-B3 Manual - Page 118

POST hex, Description, Initialize the APIC for P6 class CPU

|

UPC - 818313012272

View all Gigabyte GA-P67A-UD7-B3 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 118 highlights

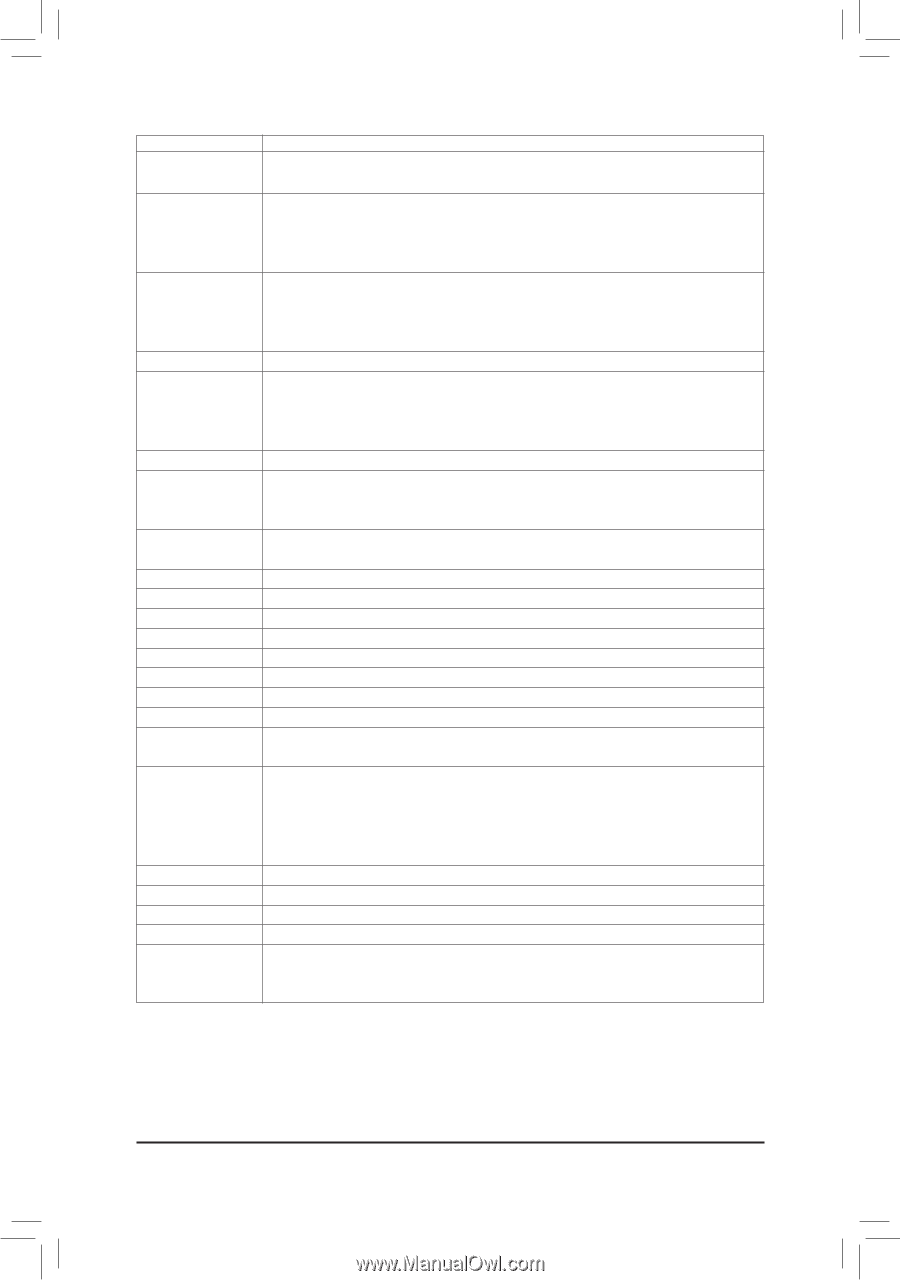

POST (hex) 24h 25h 26h 27h 29h 2Bh 2Dh 33h 35h 37h 39h 3Ch 3Eh 40h 43h 47h 49h 4Eh 50h 52h 53h 55h 57h Description Prepare BIOS resource map for PCI & PnP use. If ESCD is valid, take into consideration of the ESCD's legacy information Early PCI initialization: - Enumerate PCI bus number - Assign memory & I/O resource - Search for a valid VGA device & VGA BIOS, and put it into C000:0 1. If Early_Init_Onboard_Generator is not defined Onboard clock generator initialization. Disable respective clock resource to empty PCI & DIMM slots 2. Init onboard PWM 3. Init onboard H/W monitor devices Initialize INT 09 buffer 1. Program CPU internal MTRR for 0-640K memory address 2. Initialize the APIC for Pentium class CPU 3. Program early chipset according to CMOS setup Example: onboard IDE controller 4. Measure CPU speed Invoke video BIOS 1. Initialize double-byte language font (optional) 2. Put information on screen display, including Award title, CPU type, CPU speed, full screen logo Reset keyboard if Early_Reset_KB is defined e.g. Winbond 977 series Super I/O chips. See also POST 63h Test DMA Channel 0 Test DMA Channel 1 Test DMA page registers Test 8254 Test 8259 interrupt mask bits for channel 1 Test 8259 interrupt mask bits for channel 2 Test 8259 functionality Initialize EISA slot 1. Calculate total memory by testing the last double word of each 64K page 2. Program write allocation 1. Program MTRR of M1 CPU 2. Initialize L2 cache for P6 class CPU & program CPU with proper cacheable range 3. Initialize the APIC for P6 class CPU 4. On MP platform, adjust the cacheable range to smaller one in case the cacheable ranges between each CPU are not identical Initialize USB Keyboard & Mouse Test all memory (clear all extended memory to 0) Clear password according to H/W jumper (optional) Display number of processors (multi-processor platform) 1. Display PnP logo 2. Early ISA PnP initialization - Assign CSN to every ISA PnP device Appendix - 118 -