Intel 945G User Manual - Page 34

Intel, 945G Express Chipset Development Kit User's Manual, Table 11, Port 80h POST Codes - sata

|

UPC - 735858177825

View all Intel 945G manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 34 highlights

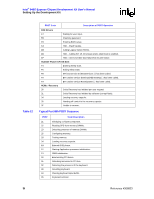

Intel® 945G Express Chipset Development Kit User's Manual Setting Up the Development Kit Table 11 Range E0-FF / F0-FF E0 - EE EF boot/S3 Processor exception. Miscellaneous codes. Resume failure. Category/Subsystem Port 80h POST Codes POST Code Host Processor 10 11 12 13 Chipset 21 Memory 22 23 24 25 26 27 28 PCI Bus 50 51 52 53-57 USB 58 59 ATA/ATAPI/SATA 5A 5B SMBus 5C 5D Local Console 70 71 Description of POST Operation Power-on initialization of the host processor (boot strap processor). Host processor cache initialization (including APs). Starting application processor initialization. SMM initialization. Initializing a chipset component. Reading SPD from memory DIMMs. Detecting presence of memory DIMMs. Programming timing parameters in memory controller and DIMMs. Configuring memory. Optimizing memory settings. Initializing memory, such as ECC init. Testing memory. Enumerating PCI buses. Allocating resources to PCI bus. Hot Plug PCI controller initialization. Reserved for PCI bus. Resetting USB bus. Reserved for USB. Resetting PATA/SATA bus and all devices. Reserved for ATA. Resetting SMBUS. Reserved for SMBUS. Resetting the VGA controller. Disabling the VGA controller. 34 Reference #308823