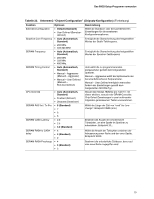

Intel D865GRH D865GRH_ProductGuide01_German. - Page 73

Tabelle 23. Untermen, Chipset Configuration, Chipsatz-Konfiguration

|

View all Intel D865GRH manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 73 highlights

Das BIOS-Setup-Programm verwenden Tabelle 23. Untermenü "Chipset Configuration" (Chipsatz-Konfiguration) (Fortsetzung) Funktion Extended Configuration Graphics Core Frequency SDRAM Frequency SDRAM Timing Control Optionen • Default (Standard) • User Defined (Benutzerdefiniert) • Auto (Automatisch, Standard) • 266 MHz • 333-320 MHz • Auto (Automatisch, Standard) • 266 MHz • 333 MHz • 400 MHz • Auto (Automatisch, Standard) • Manual - Aggressive (Manuell - Aggressiv) • Manual - User Defined (Manuell - Benutzerdefiniert) CPC Override • Auto (Automatisch, Standard) • Enabled (Aktiviert) • Disabled (Deaktiviert) SDRAM RAS Act. To Pre. • 8 (Standard) • 7 • 6 • 5 SDRAM CAS# Latency • 2.0 • 2.5 • 3.0 (Standard) SDRAM RAS# to CAS# delay • 4 • 3 (Standard) • 2 SDRAM RAS# Precharge • 4 • 3 (Standard) • 2 Beschreibung Wählt die Standard- oder benutzerdefinierten Einstellungen für die erweiterten Konfigurationsoptionen. Ermöglicht die Überschreitung des festgestellten Wertes der Grafik-Taktfrequenz. Ermöglicht die Überschreitung des festgestellten Wertes der Speicher-Taktfrequenz. Auto wählt die zu programmierenden Zeitparameter gemäß dem festgestellten Speicher. Manual - Aggressive wählt die Spitzenwerte der benutzerdefinierbaren Zeitparameter. Manual - User Defined ermöglicht manuelles Ändern der Einstellungen gemäß dem festgestellten SDRAM-Typ. Steuert den Modus "Befehle pro Takt/1n". Ist dieser aktiviert, versucht der DRAM-Controller, Chip-Select-Zuweisungen in zwei aufeinander folgenden gemeinsamen Takten vorzunehmen. Wählt die Länge der Zeit von "read" bis "prechange". Entspricht tRAS (min.) Bestimmt die Anzahl der erforderlichen Taktzyklen, um eine Spalte im Speicher zu adressieren. Entspricht CL. Wählt die Anzahl der Taktzyklen zwischen der Adressierung einer Reihe und der einer Spalte. Entspricht tRCD. Bestimmt die erforderliche Zeitdauer, bevor auf eine neue Reihe zugegriffen wird. 73