Intel S1200BT Technical Product Specification - Page 40

Optional Intel, SAS RAID Module, Integrated Baseboard Management Controller - s1200btl two beeps then three beeps

|

View all Intel S1200BT manuals

Add to My Manuals

Save this manual to your list of manuals |

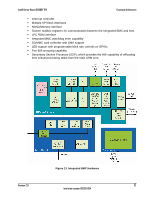

Page 40 highlights

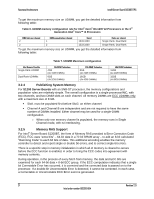

Functional Architecture Intel® Server Board S1200BT TPS During the pre-boot phase, the BIOS automatically supports the hot addition and hot removal of USB devices and a short beep is emitted to indicate such an action. For example, if a USB device is hot plugged, the BIOS detects the device insertion, initializes the device, and makes it available to the user. During POST, when the USB controller is initialized, it emits a short beep for each USB device in the system as if they were all just "hot added". Only on-board USB controllers are initialized by BIOS. This does not prevent the operating system from supporting any available USB controllers including add-in cards. 3.4.5.2 Legacy USB Support The BIOS supports PS/2 emulation of USB keyboards and mouse. During POST, the BIOS initializes and configures the root hub ports and searches for a keyboard and/or a mouse on the USB hub and then enables the devices that are recognized. 3.5 Optional Intel® SAS RAID Module The Intel® Server Board S1200BTL provides a SAS Mezzanine slot (J2H1) for the installation of an optional Intel® SAS RAID Module. Once the optional Intel® SAS Entry RAID Module is detected, the x4 PCI Express* links from the chipset to the SAS Mezzanine slot. Three modules are supported in this platform: AXXRMS2AF040, AXXRMS2LL040 and AXX4SASMOD. 3.6 Integrated Baseboard Management Controller The Intel® Server Board S1200BTL has the highly integrated single-chip baseboard management controller based on ServerEngines* Pilot III, but Intel® Server Board S1200BTS does not have the integrated baseboard management control. This Intel® Integrated BMC contains the following integrated subsystems and features. The following is a summary of the BMC management hardware features used by the BMC: 400MHz 32-bit ARM9 processor with memory management unit (MMU) Two independent10/100/1000 Ethernet Controllers with RMII (Reduced Media Independent Interface)/RGMII(Reduced Gigabit Media-Independent Interface) support DDR2/3 16-bit interface with up to 800 MHz operation 12 10-bit Analog to Digital Converters Sixteen fan tachometers Eight Pulse Width Modulators (PWM) Chassis intrusion logic JTAG Master Eight I2C interfaces with master-slave and SMBus timeout support. All interfaces are SMBus 2.0 compliant. Parallel general-purpose I/O Ports (16 direct, 32 shared) Serial general-purpose I/O Ports (80 in and 80 out) Three UARTs Platform Environmental Control Interface (PECI) Six general-purpose timers 28 Revision 2.0 Intel order number G13326-004