Oki ML421 Maintenance Manual - Page 127

Circuit Description

|

View all Oki ML421 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 127 highlights

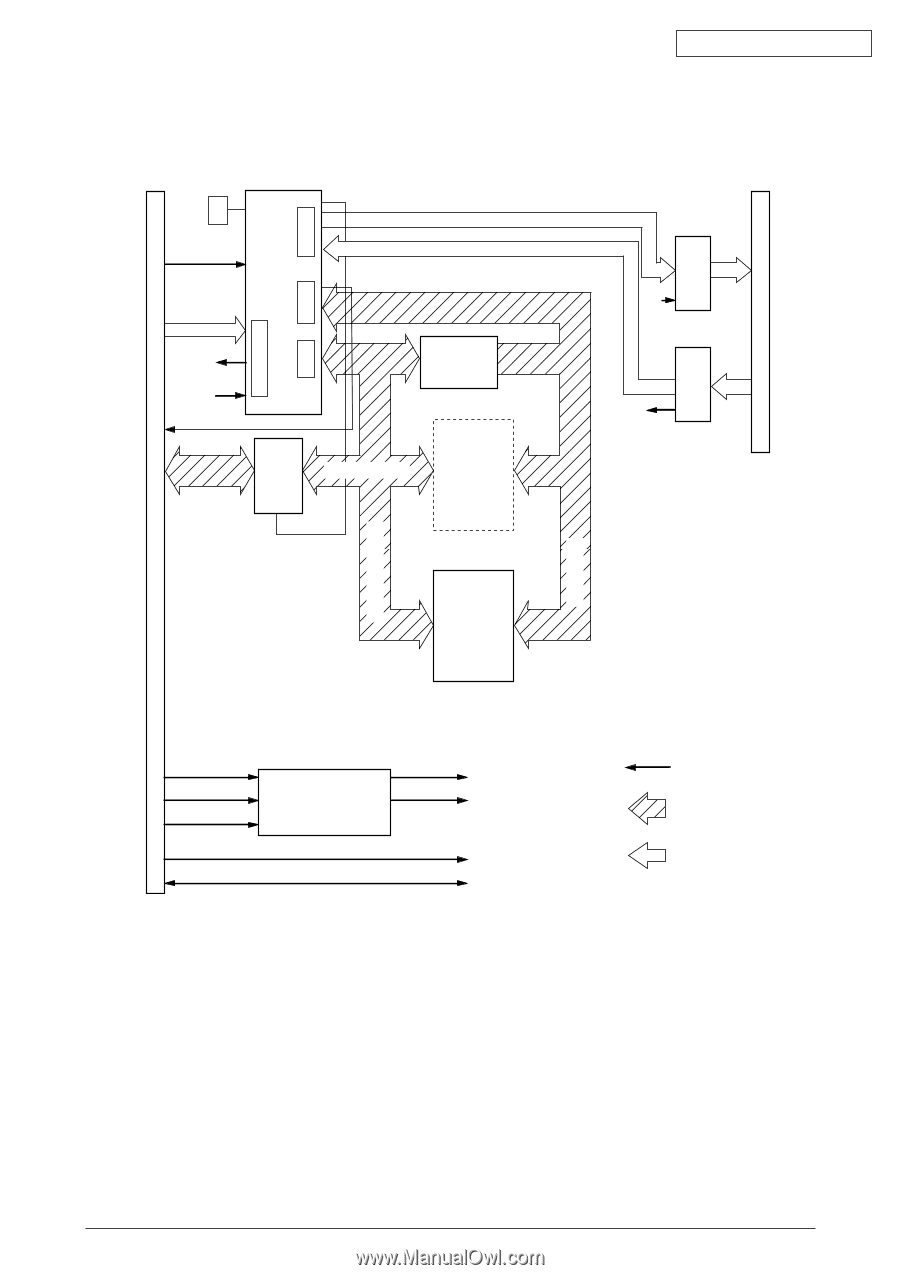

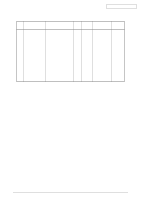

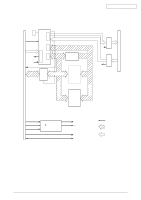

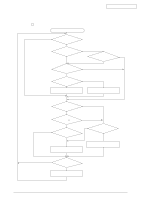

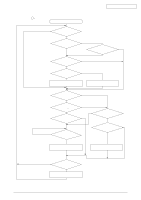

2.2 Circuit Description A block diagram is shown in Figure C-1. 80C51 RST OCS P1 P3 P0 P2 TD RD IF WR ADR latch LS245 DB0 to DB9 ROM 64Kbit Receiver Driver Oki Data CONFIDENTIAL CN1 75188 TD 75189 RD ADR bus ADR/data bus RAM 64Kbit +5 VD +12VDC -8VDC +5 V ±9 V power supply circuit +9 V -9 V +5V 0V Figure C-1 Block Diagram Serial data control line Bus line Control line 2.2.1 Operation at power on After power is turned on, an RST OUT signal is sent from the printer control board to reset the printer. When the reset is canceled, the 80C51 CPU performs initialization. Initialization consists of setting the 80C51 timer, and setting the serial mode. 2.2.2. RS-232C interface The DTR, SSD, TD and RTS signals output by the 80C51 are converted to RS-232C signals by line driver 75188 (Q1) and sent to the interface. In addition, signals DSR, CTS, CD, and RD on the RS232C interface are converted to TTL level by line receiver 75189 (Q2) and input to the 80C51. 42113901 Rev.2 127 /