Seagate ST3400620A Serial ATA Native Command Queuing (670K, PDF) - Page 7

Status Return, DMA Setup FIS

|

UPC - 000068213367

View all Seagate ST3400620A manuals

Add to My Manuals

Save this manual to your list of manuals |

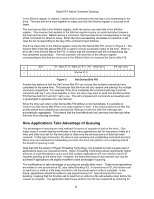

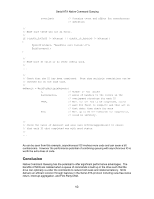

Page 7 highlights

Serial ATA Native Command Queuing To program the DMA engine for a data transfer, the drive issues a DMA Setup FIS to the host, shown in Figure 2. There are a few key fields in the DMA Setup FIS that are important for programming the DMA engine. 0 Reserved (0) 1 2 3 4 5 6 Reserved (0) A I D Reserved (0) 0 0 Reserved (0) DMA Buffer Offset DMA Transfer Count Reserved (0) FIS Type (41h) TAG Figure 2 DMA Setup FIS The TAG field identifies the tag of the command that the DMA transfer is for. For host memory protection from a rogue device, it is important to not allow the drive to indiscriminately specify physical addresses to transfer data to and from in host memory. The tag acts as a handle to the physical memory buffer in the host such that the drive does not need to have any knowledge of the actual physical memory addresses. Instead, the host uses the tag to identify which PRD table to use for the data transfer and programs the DMA engine accordingly. The DMA Buffer Offset field is used to support out-of-order data delivery, also referred to as nonzero buffer offset within the specification. Non-zero buffer offset allows the drive to transfer data out-of-order or in-order but in multiple pieces. The DMA Transfer Count field identifies the number of bytes to be transferred. The D bit specifies the direction of the transfer (whether it is a read or a write). The A bit is an optimization for writes called Auto-Activate, which can eliminate one FIS transfer during a write command. One important note for HBA designers is that new commands cannot be issued between the DMA Setup FIS and the completion of the transfer of the data for that DMA Setup FIS. It is important that the drive is not interrupted while actively transferring data since taking a new command may cause a hiccup in the transfer of data. Thus this restriction was added explicitly in the NCQ definition. Analogously, drives cannot send a Set Device Bits FIS before the completion of the data transfer for that DMA Setup FIS. There is one exemption to this restriction; if an error is encountered before all of the data is transferred, a drive may send a Set Device Bits to terminate the transfer with error status. After the DMA Setup FIS is issued by the drive, data is transferred using the same FISes that are used in a non-queued DMA data transfer operation. Status Return Command status return is race-free and allows interrupts for multiple commands to be aggregated. The host and the drive work in concert to achieve race-free status return without handshakes between the host and drive. Communication between the host and drive about which commands are outstanding is handled through a 32-bit register in the host called SActive. The SActive register has one bit allocated to each possible tag, i.e. bit x shows the status of the command with tag x. If a bit in the SActive register is set, it means that a command with that tag is outstanding in the drive (or a command with that tag is about to be issued to the drive). If a bit 7