Sony A941 Service Manual - Page 8

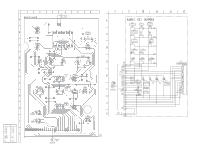

Cat93c46ki Base Main Board

|

View all Sony A941 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 8 highlights

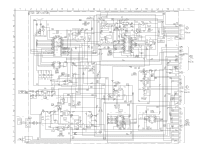

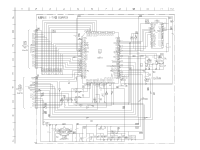

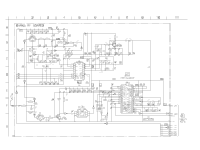

• IC Block Diagrams U1 U2765B-AFSG3 (BASE RF Board) U1 U2765B-AFSG3 (HAND RF Board) VCC2 LO REF LO IN GND2 NC VCC3 LIM1 OUT GND3 LIM2 IN LIM2 REF GND4 DEM NTANK DEM TANK DEM OUT 28 27 26 25 24 23 22 21 20 19 18 17 16 15 LOCAL OSC BUFFER MIX LIMITER AMP LIMITER AMP DEMODULATOR VCC/2 RSSI COMPARATOR SLICER + - + - A1 1 2 3 4567 8 9 10 11 12 13 14 NC A1 REF A1 IN GND1 MIX OUT VCC1 MIX NOUT LIM1 REF LIM1 IN RSSI DATA OUT COM NIN COM IN SL IN FIN2 VCC CP2 GND SW XIN XOUT BO U3 TB31202BFN-EL (HAND RF Board) U10 TB31202BFN-EL (BASE RF Board) 16 15 1/2 1 -------- BUF 32, 33 1 -------- BUF 32, 33 1/2 14 13 PHASE COMPARATOR OUTPUT PROGRAMABLE DIVIDER PROGRAMABLE DIVIDER PHASE COMPARATOR OUTPUT 12 11 SWITCH L. OSC 10 9 BUF 1/2 REFERENCE DIVIDER LOCK DET CONTROL CIRCUIT 1 2 3 4 5 6 7 8 STB DATA CK LD GND DI CP1 VCC FIN1 CS SK U3 CAT93C46KI (BASE MAIN Board) GND ORG NC VCC 876 MEMORY ARRAY 128X8 bit/ 64X16 bit DATA REGISTER DECODE & CONTROL LOGIC CLOCK GENERATOR 5 HIGH VOLTAGE GENERATOR ADDRESS DECODER BUFFER 1 2 3 4 DO U6 KA8602D (BASE MAIN Board) IN+ 1 IN- 2 OUT1 3 VCC 4 BIAS CIRCUIT 8 RIPPLE REJECTION 7 MUTE -+ AMP1 -+ AMP2 6 OUT2 5 GND - 43 - U4 TA31103F (BASE MAIN Board) U7 TA31103F (HAND MAIN Board) VCC PRE NF PRE OUT E-RECT EXP OUT RIN RO1 RO2 COMP MUTE EXP MUTE THROUG VREF 24 23 22 21 - ∆G + PRE AMP VREF FILTER AMP 2 FILTER AMP 1 20 19 18 17 16 15 14 13 EXP SUM MUTE AMP - + THROUGH VREF - + RO1 VREF AMP THROUG - + RO2 VREF AMP SWITCH CONTROL IN 2 VREF AMP COMP MUTE + SUM VREF AMP MIC AMP + - - + + + - - - 1 23 45 ∆G 6 7 8 9 10 11 12 MIC OUT MIC NF MIC IN GND C-NF C-RECT IN2 COMP OUT FIL1 IN FIL2 OUT FIL2 IN FIL1 OUT U10 MC74HC595AF (BASE MAIN Board) SERIAL DATA RESET CLOCK SHIFT LATCH CLOCK OUTPUT ENABLE SERIAL DATA INPUT OUTPUT PARALLEL DATA QA A 16 15 14 13 12 11 VCC SHIFT REGISTER 10 9 SQH QB LATCH QH QG QF QE QD QC GND 1 2 34 5 67 8 PARALLEL DATA OUTPUT OUTPUT U11 LP2953IM (HAND MAIN Board) GND 1 NC 2 OUTPUT 3 SENSE 4 SHUT DOWN 5 ERROR AMP 16 GND 15 INPUT 14 FEEDBACK 13 5V TAP + - - + - + - + ERROR 6 NC 7 GND 8 SHUT DOWN COMPARATOR DROP OUT DETECTION AMP AUXILLARY COMPARATOR 12 VREF 1.23V 11 COMP IN 10 COMP OUT 9 GND - 44 -