ASRock Fatal1ty X470 Gaming-ITX/ac User Manual - Page 72

AMD CBS

|

View all ASRock Fatal1ty X470 Gaming-ITX/ac manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 72 highlights

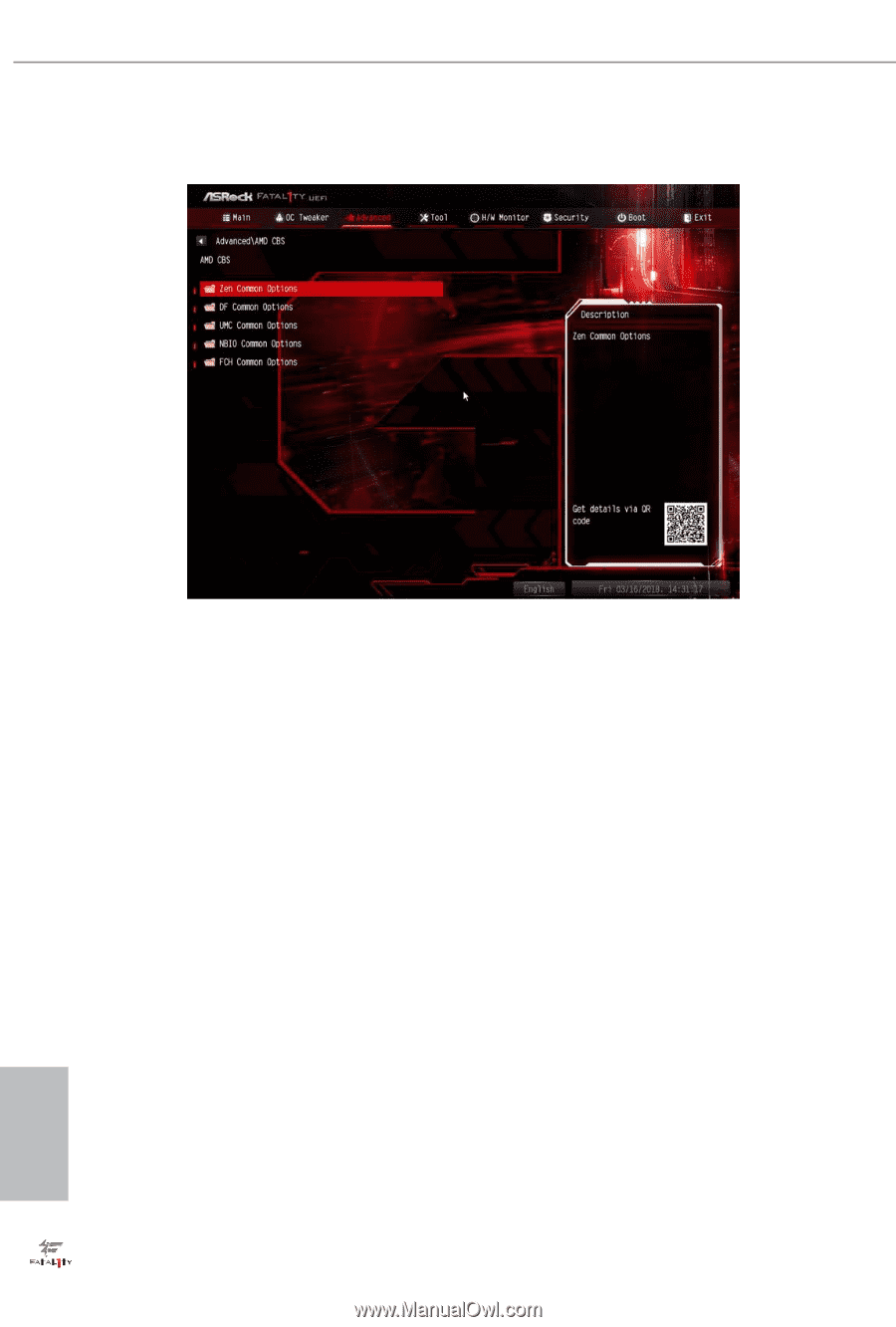

4.4.7 AMD CBS Zen Common Options RedirectForReturnDis From a workaround for GCC/C000005 issue for XV Core on CZ A0, setting MSRC001_1029 Decode Configuration (DE_CFG) bit 14 [DecfgNoRdrctForReturns] to 1. L2 TLB Associativity 0 - L2 TLB ways [11:8] are fully associative. 1 - =L2 TLB ways [11:8] are 4K-only. Platform first Error Handling Enable/disable PFEH, cloak individual banks, and mask deferred error interrupts from each bank. Core Performance Boost Disable CPB. Enable IBS Enables IBS through MSRC001_1005[42] and disables SpecLockMap through MSRC001_1020[54]. Global C-state Control Controls IO based C-state generation and DF C-states. 62 English

English

62

4.4.7 AMD CBS

Zen Common Options

RedirectForReturnDis

From a workaround for GCC/C000005 issue for XV Core on CZ A0, setting MSRC001_1029

Decode Configuration (DE_CFG) bit 14 [DecfgNoRdrctForReturns] to 1.

L2 TLB Associativity

0 - L2 TLB ways [11:8] are fully associative.

1 - =L2 TLB ways [11:8] are 4K-only.

Platform first Error Handling

Enable/disable PFEH, cloak individual banks, and mask deferred error interrupts from each

bank.

Core Performance Boost

Disable CPB.

Enable IBS

Enables IBS through MSRC001_1005[42] and disables SpecLockMap through

MSRC001_1020[54].

Global C-state Control

Controls IO based C-state generation and DF C-states.