Asus M2N32-SLI Premium VISTA Edition Motherboard Installation Guide - Page 95

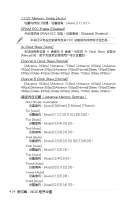

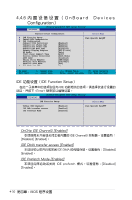

DRAM 計時控制(DRAM Timing Control)

|

View all Asus M2N32-SLI Premium VISTA Edition manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 95 highlights

Tref [Auto Auto] [Undef] [7.8 us] [3.9 us]。 Trfc [Auto Auto] [0] [1] [2] [3]。 DRAM Termination [Auto Auto] [Disabled] [75 ohms] [150 ohms] [50 ohms]。 Max Async Latency [Auto Auto] [0 ns] [1 ns] [2 ns] [3 ns]~[14 ns] [15 ns]。 R/W Queue Bypass Auto] [2x] [4x] [8x] [16x]。 Dynamic Idle Cycle Counter [Auto Auto] [Disabled] [Enabled]。 Idle Cycle Limit [Auto Auto] [0 cycles] [4 cycles] [8 cycles] [16 cycles] [32 cycles] [64 cycles] [128 cycles] [256 cycles]。 DCQ Bypass Maximum [Auto Auto] [0x] [1x] [2x] [3x]~[14x] [15x]。 DRAM Burst Length [Auto Auto] [64-byte] [32-byte]。 RdPadRcvFIFO Delay [Auto Auto] [1.5] [2] [2.5] [3] [3.5]。 Disable Jitter [Auto Auto] [OFF] [ON]。 DRAM Bank Interleaving [Enabled Disabled] [Enabled]。 Bank Swizzle Mode [Enabled Disabled] [Enabled]。 DRAM DRAM Timing Control) CKE Fine Delay [Auto Auto] [No delay] [1/64 MEMCLK delay] [2/64 MEMCLK delay] [3/64 MEMCLK delay] [4/64 MEMCLK delay] [5/64 MEMCLK delay]...[30/64 MEMCLK delay] [31/64 MEMCLK delay]。 CKE Setup Time [Auto Auto] [1/2 MEMCLK] [1 MEMCLK]。 CS/ODT Fine Delay [Auto] 華碩 M2N32-SLI Premium Vista Edition 4-25