Dell PowerEdge R220 Statement of Volatility Dell PowerEdge R220 - Page 2

Purpose? e.g. boot, How is data input to this memory?, How is this memory write protected? - drivers

|

View all Dell PowerEdge R220 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 2 highlights

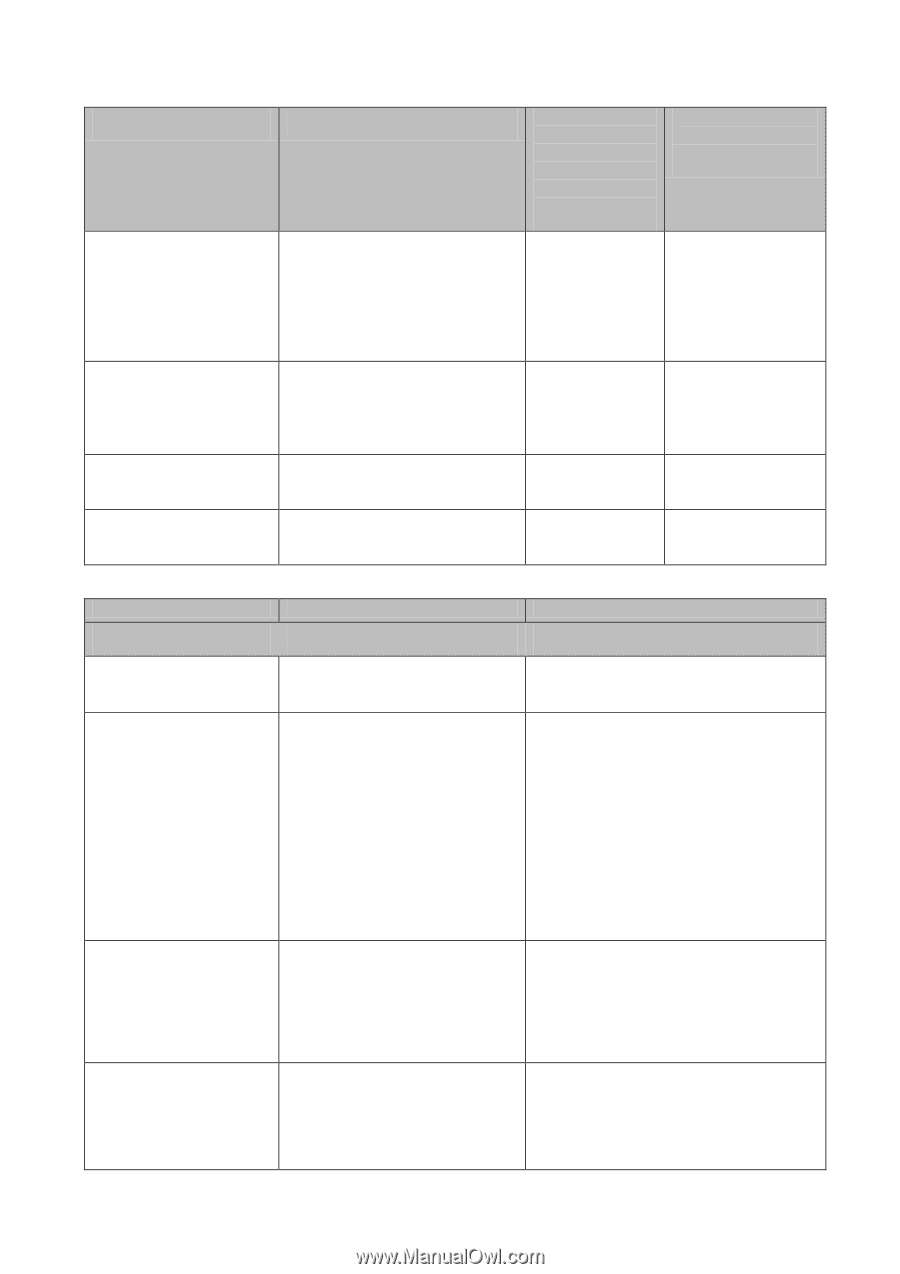

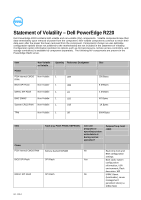

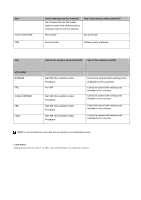

Item BMC EMMC System CPLD RAM TPM Type (e.g. Flash PROM, EEPROM) Can user programs or operating system write data to it during normal operation? Purpose? (e.g. boot code) EMMC NAND Flash RAM Address, iDRAC boot variables), lifecycle log cache, virtual planar FRU and EPPID, rac log, System Event Log, JobStore, iDRAC Secure Boot Code, No Operational iDRAC FW, Lifecycle Controller (LC) USC partition, LC service diags, LC OS drivers, USC firmware No Not utilized EEPROM No Data Protection Item Planer PCH Internal CMOS RAM BIOS SPI Flash iDRAC SPI Flash BMC EMMC How is data input to this memory? How is this memory write protected? BIOS default settings, which can be altered by F2 Setup Menu during POST Loading flash memory requires a vendor-provided firmware file and loader program which is executed by booting up the system from a USB key (or floppy). In addition, an OSbased update package executable containing the firmware file can be run. A system loaded with arbitrary data in BIOS FLASH memory will not operate. Not accessible Software write protected Loading flash memory requires a vendor provided firmware file and loader program. System loaded with arbitrary data in flash memory would not operate. Software write protected Loading flash memory requires a vendor provided firmware file and loader program which is executed by booting up the system from a floppy or OS-based executable containing Software write protected