Dell PowerEdge T430 Dell PowerEdge T430 - Statement of Volatility - Page 7

Package from LC or OS - ram

|

View all Dell PowerEdge T430 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 7 highlights

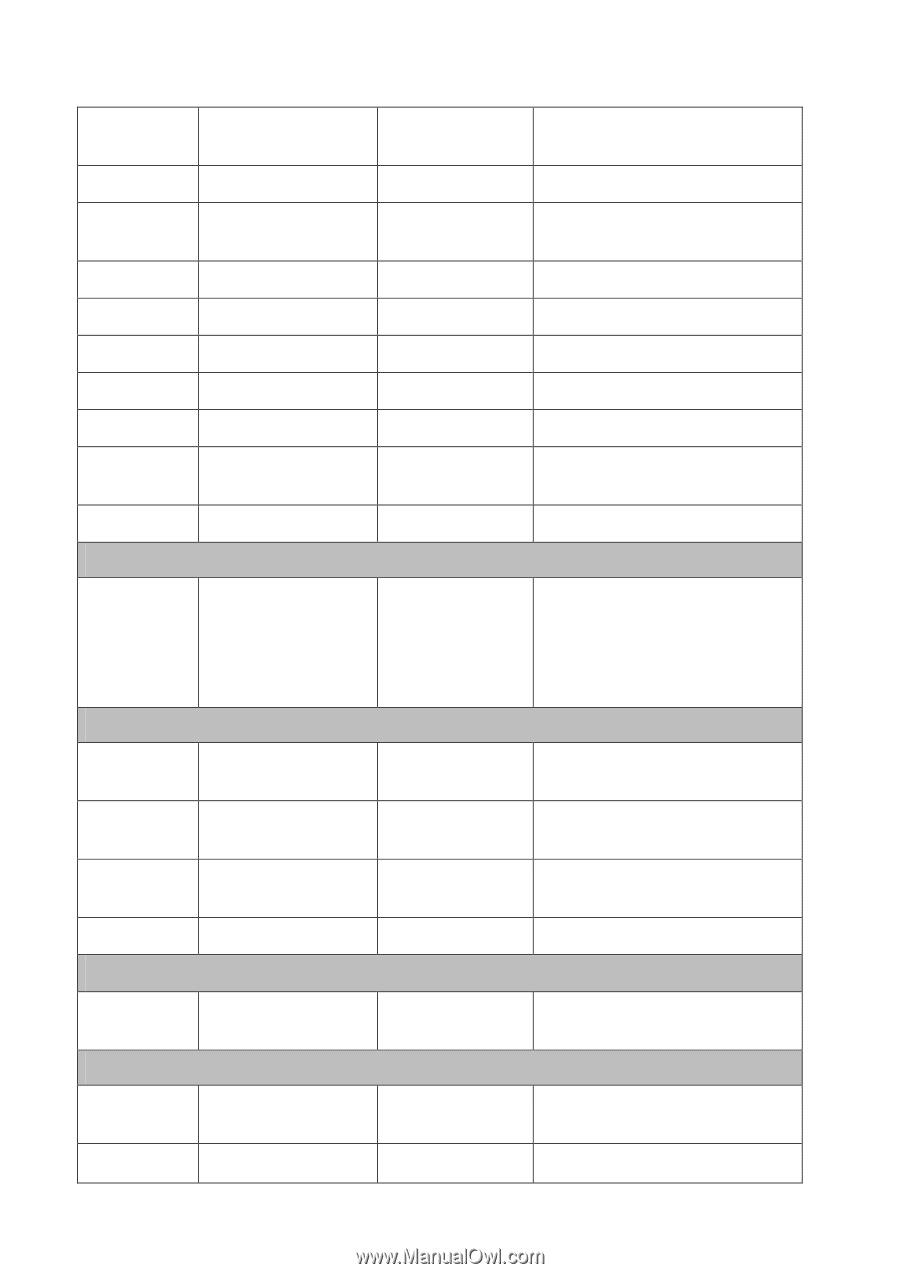

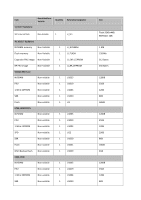

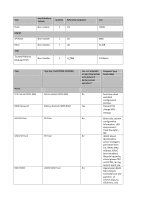

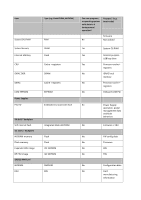

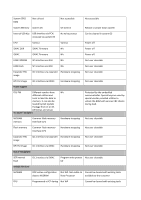

System CPLD RAM Not utilized Not accessible Not accessible System Memory System OS OS Control Reboot or power down system Internal USB Key USB interface via PCH. Accessed via system OS No write protect Can be cleared in system OS CPU Various Various Power off iDRAC DDR iDRAC Firmware NA Power off iDRAC iDRAC Firmware NA Power off LOM EEPROM SPI interface via i350 NA Not user clearable LOM Flash SPI interface via i350 NA Not user clearable Expander FRU image I2C interface via expander Hardware strapping Not user clearable BP FRU image I2C interface via iDRAC Hardware strapping Not user clearable Power Supplies PSU FW Different vendors have NA different utilities and tools to load the data to memory. It can also be loaded by Dell Update Package from LC or OS (Windows and Linux) 5U 16x2.5" Backplane Protected by the embedded microcontroller. Special keys are used by special vendor provided utilities to unlock the ROM with various CRC checks during load. NVSRAM memory Common Flash memory Interface (CFI) Hardware strapping Not user clearable Flash memory Common Flash memory Interface (CFI) Hardware strapping Not user clearable Expander FRU image I2C interface via Expander Hardware strapping Not user clearable BP FRU image I2C interface via iDRAC Hardware strapping Not user clearable 8x3.5" Backplane SEP internal flash I2C interface via iDRAC Program write protect Not user clearable bit SAS12G HBA Card NVSRAM ROC writes configuration Not WP. Not visible to Cannot be cleared with existing tools data to NVSRAM Host Processor available to the customer FRU Programmed at ICT during Not WP Cannot be cleared with existing tools