Foxconn Cinema II Premium English Manual. - Page 48

Memory Features

|

View all Foxconn Cinema II Premium manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 48 highlights

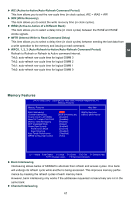

► tRC (Active-to-Active/Auto-Refresh Command Period) This item allows you to set the row cycle time (in clock cycles). tRC = tRAS + tRP. ► tWR (Write Recovery) This item allows you to select the write recovery time (in clock cycles). ► tRRD (Active-to-Active of a Different Bank) This item allows you to select a delay time (in clock cycles) between the RAS# and RAS# strobe signals. ► tWTR (Internal Write to Read Command Delay) This item allows you to select a delay time (in clock cycles) between sending the last data from a write operation to the memory and issuing a read command. ► tRFC0, 1, 2, 3 (Auto-Refresh-to-Active/Auto-Refresh Command Period) Refresh to Refresh or Refresh to Active command interval. Trfc3: auto-refresh row cycle time for logical DIMM 3 Trfc2: auto-refresh row cycle time for logical DIMM 2 Trfc1: auto-refresh row cycle time for logical DIMM 1 Trfc0: auto-refresh row cycle time for logical DIMM 0 3 Memory Features CMOS Setup Utility - Copyright (C) 1985-2009, American Megatrends, Inc. Memory Features Memory Features Help Item Bank Interleaving [Auto] Sligthly improves Channel Interleaving [XOR of Address bit] memory performance Enable Clock to All DIMMs [Disabled] MemCLK Tristate C3/ATLVID [Disabled] Memory Hole Remapping [Enabled] DCT Unganged Mode [Always] Power Down Enable [Enabled] Power Down Mode [Channel] Page Smashing [Disabled] Auto Tweak Performance [Disabled] DRAM Config_High Control [Auto] Move Enter:Select +/-/:Value F10:Save ESC:Exit F1:General Help F2/F3:Change Colors F9:Optimized Defaults ► Bank Interleaving Interleaving allows banks of SDRAM to alternate their refresh and access cycles. One bank will undergo its refresh cycle while another is being accessed. This improves memory performance by masking the refresh cycles of each memory bank. However, bank interleaving only works if the addresses requested consecutively are not in the same bank. ► Channel Interleaving 41