Gigabyte GA-EP45T-UD3LR Manual - Page 42

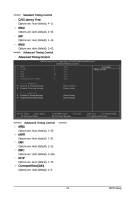

Channel A/B Timing Settings

|

UPC - 818313006844

View all Gigabyte GA-EP45T-UD3LR manuals

Add to My Manuals

Save this manual to your list of manuals |

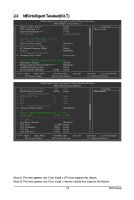

Page 42 highlights

>>>>> Channel A/B Channel A/B Timing Settings CMOS Setup Utility-Copyright (C) 1984-2008 Award Software Channel A Timing Settings x Static tRead Value x tRD Phase0 Adjustment x tRD Phase1 Adjustment x tRD Phase2 Adjustment x tRD Phase3 Adjustment 6 Auto 1 Auto 0 Auto 1 Auto 1 Auto Item Help Menu Level x Trd2rd(Different Rank) x Twr2wr(Different Rank) x Twr2rd(Different Rank) x Trd2wr(Same/Diff Rank) 6 Auto 6 Auto 5 Auto 8 Auto x DIMM1 Clock Skew Control x DIMM2 Clock Skew Control x DDR Write Leveling x DDR Write Training Auto Auto Auto Auto Move Enter: Select F5: Previous Values +/-/PU/PD: Value F10: Save F6: Fail-Safe Defaults Static tRead Value Options are: Auto (default), 1~15. tRD Phase0 Adjustment Options are: Auto (default), 0-Normal, 1-Advanced. tRD Phase1 Adjustment Options are: Auto (default), 0-Normal, 1-Advanced. tRD Phase2 Adjustment Options are: Auto (default), 0-Normal, 1-Advanced. tRD Phase3 Adjustment Options are: Auto (default), 0-Normal, 1-Advanced. Trd2rd(Different Rank) Options are: Auto (default), 1~15. Twr2wr(Different Rank) Options are: Auto (default), 1~15. Twr2rd(Different Rank) Options are: Auto (default), 1~15. Trd2wr(Same/Diff Rank) Options are: Auto (default), 1~15. DIMM1 Clock Skew Control Options are: Auto (default), +800ps~-700ps. DIMM2 Clock Skew Control Options are: Auto (default), +800ps~-700ps. ESC: Exit F1: General Help F7: Optimized Defaults GA-EP45T-UD3LR Motherboard - 42 -