HP ML350 ISS Technology Update, Volume 8, Number 4 - Page 2

Optimizing memory performance in ProLiant G6 Intel-based servers - proliant g6 memory

|

View all HP ML350 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 2 highlights

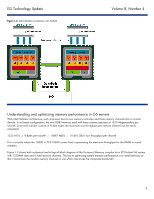

ISS Technology Update Volume 8, Number 4 Optimizing memory performance in ProLiant G6 Intel-based servers To achieve higher performance and better efficiency, the new HP ProLiant G6 servers featuring the Intel® Nehalem architecture use a memory architecture that is significantly different than previous generations of servers. Comparing traditional and non-uniform memory architecture In traditional server memory architecture, memory controllers are part of the server chipset, and physical memory is attached to these through the memory channels. This is sometimes referred to as a Uniform Memory Architecture since all processors in the system have exactly the same speed access to all of system memory through the front-side bus, the system chipset, and the memory controllers (Figure 1-1). Figure 1-1. Traditional system architecture Uniform memory architectures worked well. As system complexity increased, however, new challenges emerged. In order to support large system memory footprints, the system memory controllers needed to support 4 or more DIMM's per memory channel. The electrical loading requirements this created led to the use of fully buffered DIMMs. This solved the electrical loading problems but imposed significant additional burdens in terms of memory costs and power consumption. Overall bandwidth between the processors and memory was also limited by the bandwidth of the front-side bus. The Intel Nehalem architecture (as well as AMD Opteron architecture) has addressed these issues by using a Non-Uniform Memory Architecture (NUMA). With NUMA, each processor has its own memory controller, memory channels, and directly attached DIMMs, allowing it to directly access this memory at maximum bandwidth with no intermediate transport mechanism required (Figure 1-2). The memory attached to a given processor is still a part of the overall system memory. Other processors can access it over the new Intel® QuickPath® Interconnect links that exist between processors as well as from processors to the system chipset. 2