HP ProLiant 3000 Highly Parallel System Architecture in Compaq Servers - Page 3

Introduction Architecture Overview - price

|

View all HP ProLiant 3000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 3 highlights

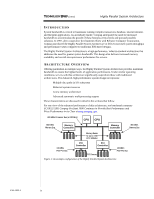

0166-0899-A TECHNOLOGY BRIEF (cont.) Highly Parallel System Architecture ... INTRODUCTION System bandwidth is critical to businesses running complex transaction, database, internet/intranet, and file/print applications. As an industry leader, Compaq anticipated the need for increased bandwidth to accommodate the growth of these business-critical tools and pursued possible solutions. In 1997, after cooperative development efforts with Reliance Computer Corporation, Compaq introduced the Highly Parallel System Architecture to deliver increased system throughput and performance when compared to traditional X86-based designs. The Highly Parallel System Architecture is a high-performance, industry-standard architecture that addresses the need for greater system bandwidth. This design also delivers increased memory scalability and overall microprocessor performance for servers. ARCHITECTURE OVERVIEW Offering parallelism in multiple ways, the Highly Parallel System Architecture provides maximum bandwidth to ensure the highest levels of application performance. Under similar operating conditions, servers with this architecture significantly outperform those with traditional architectures. This balanced, high-performance system design incorporates: • Multiple data paths in I/O subsystem • Balanced system resources • A new memory architecture • Advanced symmetric multiprocessing support These characteristics are discussed in detail in the sections that follow. For one view of the enhanced performance of this architecture, see benchmark summary ECG052/1198, Compaq ProLiant 3000 Continues to Provide Best Performance and Price:Performance in its Class at www.compaq.com. 800 MB/s Processor Bus (at 100 MHz) 800 MB/s Memory Bus Memory Controller CPU CPU Memory Controller 800 MB/s Memory Bus Memory Banks for up to 4 GB ECC SDRAM 133 MB/s Peer-PCI Bus PCI Controller PCI Controller PCI Devices 133 MB/s Peer-PCI Bus Figure 1: An example configuration of the Highly Parallel System Architecture 3