HP ProLiant DL185 Fully-Buffered DIMM technology in HP ProLiant servers - Page 7

Higher performance, Improved reliability

|

View all HP ProLiant DL185 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 7 highlights

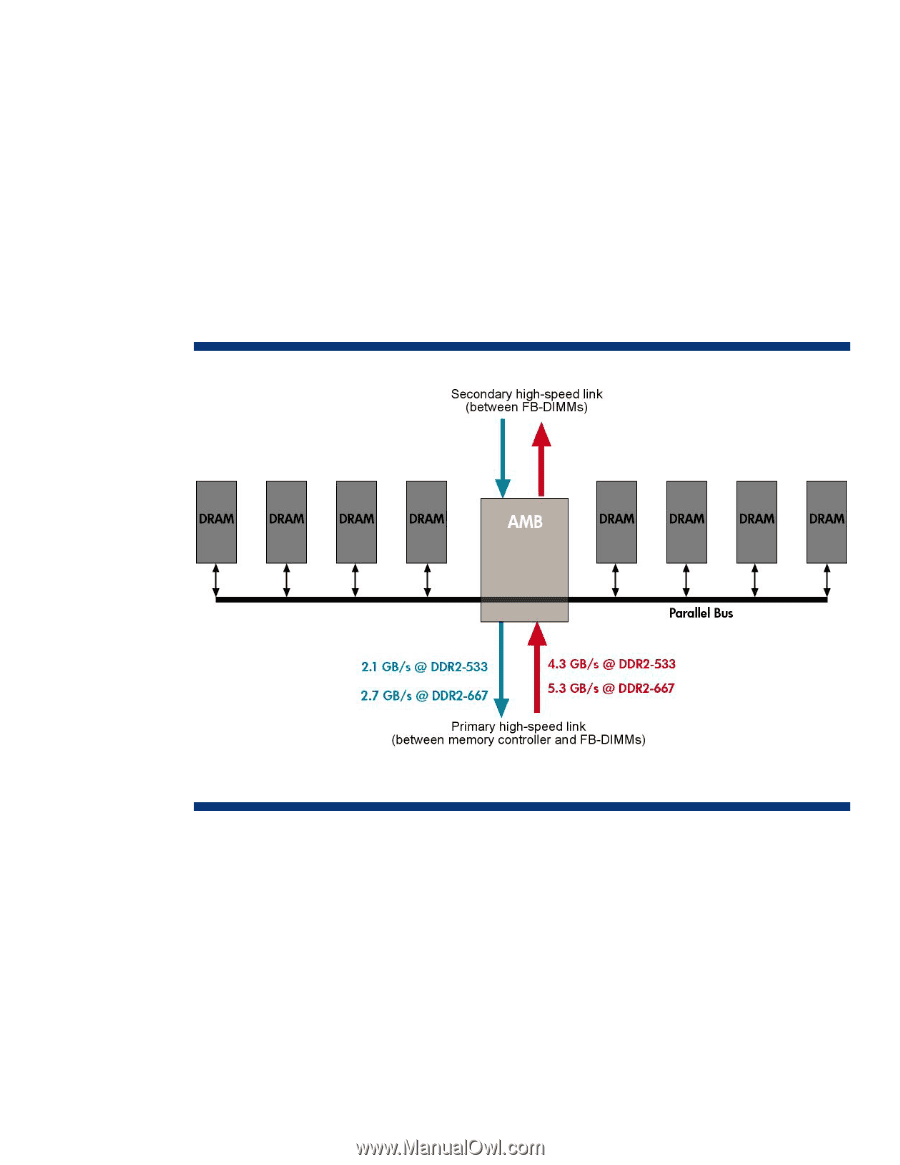

Higher performance The asynchronous serial links between the memory controller and AMB enable higher performance by the memory subsystem. The two devices operate on independent clocks, so the transmitting device embeds a bit clock with the data stream. The bit clock consists of a start bit that indicates the beginning of a chunk of information, or data word, and a stop bit that indicates the end of the data word. This eliminates skew between the clock and the data-an issue with parallel interfaces-and allows very high data rates to be achieved. As described previously, the outbound links exhibit one-half the peak theoretical throughput of the inbound links. For FB-DIMMS with DDR2-533 DRAM devices, the outbound links have a theoretical throughput of 2.1 GB/sec, or approximately one-half of 4.3-GB/s inbound links (Figure 6). Because the serial links transport write and read data simultaneously, the total theoretical throughput of the FBDIMM channel is 6.4 GB/s (2.1 GB/s plus 4.3 GB/s). When using DDR2-667 DRAM, the total theoretical throughput of the FB-DIMM channel is 8.0 GB/s (2.7 GB/s plus 5.3 GB/s) Figure 6. Theoretical throughput of the FB-DIMM channel Improved reliability FB-DIMM technology improves reliability through extended use of ECC and the introduction of a new fail-over mechanism. FB-DIMMs extend the use of ECC to protect commands and address information in the event of a soft error. This feature can help reduce instances where the soft error could disrupt server performance and reliability. A second data protection mechanism called "bit lane fail-over" correction identifies a bad data path and removes it from service. 7