HP ProLiant DL280 Technology implementation in HP ProLiant G6 Intel-based serv - Page 3

Integrated memory controller, Three-level cache hierarchy, Intel Microarchitecture Nehalem

|

View all HP ProLiant DL280 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 3 highlights

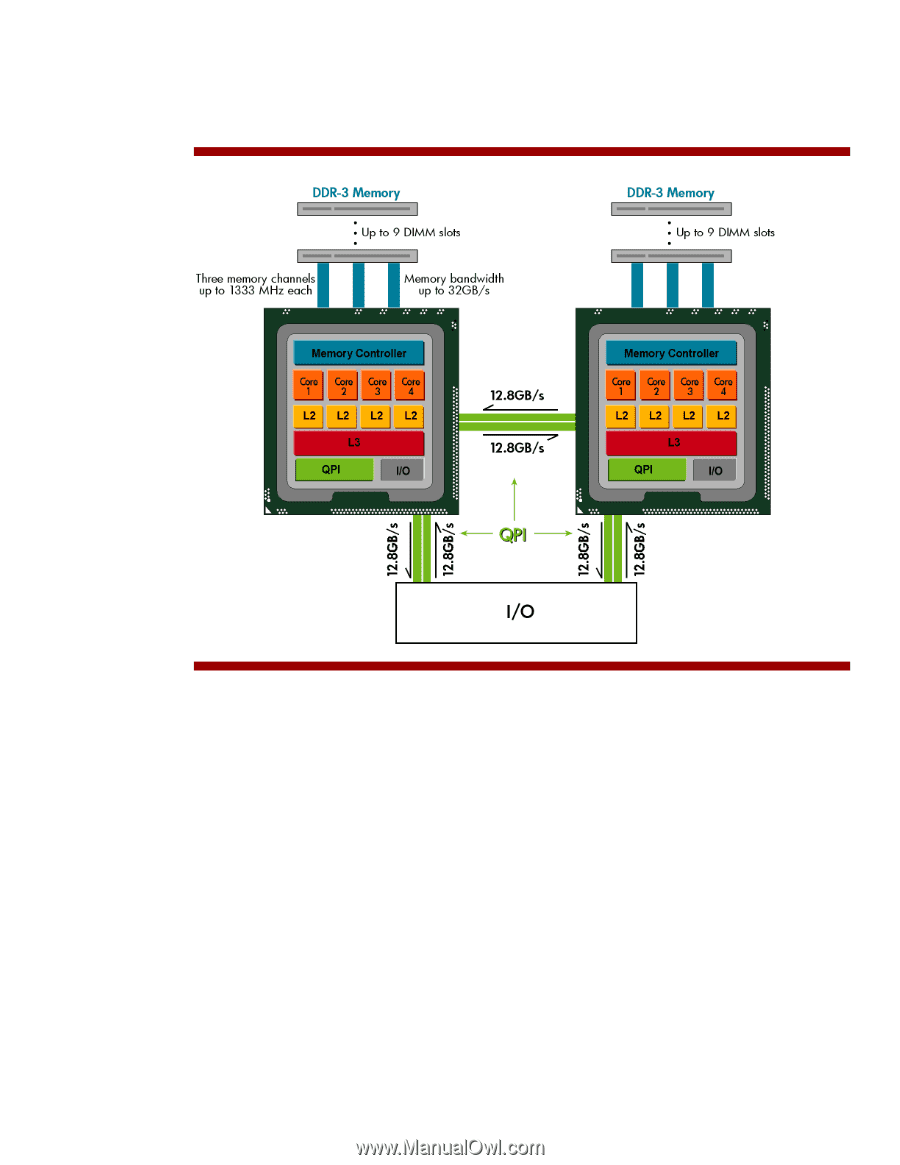

in previous-generation Intel architectures. Each QPI consists of two uni-directional links that operate simultaneously in opposite directions with a total bandwidth up to 25.6GB/s. Each uni-directional link consists of twenty 1-bit lanes that transmit up to16 data packets in multiple parallel transfers. Of the remaining lanes, one is used as a clock lane and three are used for clock or data fail-over. Figure 1. Intel Microarchitecture Nehalem Integrated memory controller One of the most notable improvements in Intel Xeon 5500 series processors is the integrated memory controller. The memory controller uses three channels (up to 1333-MHz each) to access dedicated DDR3 memory sockets. This design delivers a substantial performance improvement over previous Intel architectures that provided only two memory channels and required processors to share a single pool of system memory. HP optimized the design to support the maximum memory speed for topologies with two DIMMs per channel. The three memory channels have a total bandwidth of 32GB/s. Three-level cache hierarchy HP has implemented the three-level cache hierarchy present in each Intel Xeon 5500 series processor. This consists of an on-core 64-KB L1 cache, a separate 256-KB L2 cache for each core, and an inclusive, shared L3 cache of up to 8MB. The L3 cache duplicates the data stored in each core's L1 and L2 cache. This data duplication eliminates unnecessary searches, or snoops, to those caches and minimizes latency. Additional data tracking technology in the L3 cache ensures inter-core cache coherency. If one processor needs to access the cache or DDR3 memory of the other processor, it uses the high-speed QPI between the two processors. 3