HP Professional 5100 Highly Parallel System Architecture for Compaq Profession - Page 9

Alternative Architectures, Typical NT/X86 Architecture, Unified Memory Architecture

|

View all HP Professional 5100 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 9 highlights

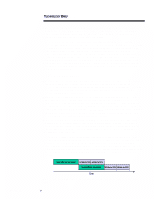

ECG066/1198 TECHNOLOGY BRIEF (cont.) ... ALTERNATIVE ARCHITECTURES Compaq is implementing this new Highly Parallel System Architecture because other architectures do not provide equal levels of bandwidth, performance, expansion, and cost effectiveness. Typical NT/X86 Architecture Most workstations in the NT/X86 market support two processors to process instructions concurrently (Figure 5). Overall system bandwidth is limited in such systems, however, because each processor must compete with the other for access to subsystems such as memory and disk. Traditional memory architectures use a single memory controller through which all memory requests are processed. Depending on implementation, the maximum bandwidth of these memory subsystems is either 267 MB/s or 533 MB/s. The actual memory throughput will be limited, however, by the same DRAM constraints identified earlier in the section "Dual Memory Buses." The new memory architecture that Compaq is implementing, on the other hand, employs dual memory controllers that can process memory requests in parallel. This design allows memory bandwidth to reach up to 1.07 GB/s-two to four times the bandwidth of other NT/X86 systems. Furthermore, with dual-peer PCI buses, high-bandwidth peripherals can be placed on separate PCI buses. CPU CPU Memory Controller PCI Controller Disk Graphics Controller PCI Slots and other Devices SCSI Controller Figure 5. Typical architecture for an X86 computer running Microsoft Windows NT. Unified Memory Architecture Silicon Graphics, Inc. touts the Unified Memory Architecture (UMA) used in their O2 workstation. Although UMA provides a cost-effective system, it does so by sacrificing performance. With SGI's UMA, the processor and graphics controller share one memory pool that is connected by a single bus with a peak bandwidth of up to 2.1 GB/s (Figure 6). As noted earlier in the section "Dual Memory Buses," the actual memory throughput will be limited by DRAM constraints. The graphics controller stores its frame buffer, Z-buffer, and textures in the common memory pool. Because the processor, the graphics controller, and the monitor compete for access to memory, however, this architecture does not deliver as much actual throughput as the new Highly Parallel System Architecture. For example, refreshing the monitor at 85 Hz at a screen resolution of 1280 x 1024 true color requires that data be transferred to the monitor at a 9