HP Visualize J210 Overview of the Visualize fx graphics - Page 7

Go to Next Article, Go to Journal Home

|

View all HP Visualize J210 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 7 highlights

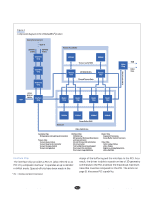

Raster Chip The raster chip rasterizes the geometry into the frame buffer. This means it determines which pixels are to be potentially modified and, if so, whether they should be modified based on various current state values (including the contents of the z buffer). The raster chip also controls access to the various buffers that make up the frame buffer. This includes the image buffer for storing the image displayed on the screen (potentially two buffers if double buffering is in effect), an overlay buffer that contains images that overlay the image buffer, the depth or z buffer for hidden surface removal, the stencil buffer,* and an alpha buffer** on the VISUALIZE fx6. To accomplish its work the raster chip performs four basic functions: H Rasterize primitives described as points, lines, or triangles H Apply fragment operations as defined by OpenGL (such as blending and raster operations) H Control of and access to buffer memory, including all the buffers described earlier H Refresh the data stream for the video chip, including handling windows and overlays. Video Chip The video chip provides video functions for controlling the data flow from the frame buffer to the display and * A stencil buffer is per pixel data that can be updated when pixel data is written and used to restrict the modification of the pixel. ** An alpha buffer contains per pixel data that describes coverage information about the pixel and can be used when blending new pixel values with the current pixel value. mapping data from values to color. The features of the video chip include: H Data mapping to colors: V Two independent 4096-by-24-bit lookup tables V Four independent 256-by-3-by-8-bit lookup tables for image planes V A bypass path for 24-bit true color data V Two independent 256-by-8-bit lookup tables for overlay planes H Digital-to-analog conversion H Video timing H Video output. Conclusion The VISUALIZE fx family of products currently has a substantial lead in not only price/performance measurements, but it also leads in performance independent of cost. For information regarding how these systems compare against the competition, visit the SPEC (an industry standard body of benchmarks) web page at: http://www.spec.org/gpc Acknowledgments We would like to thank Paul Martz for the shadow texture image (Figure 2 on page 33). Noel D. Scott Noel Scott is a senior engineer at the HP Workstation Systems Division. He is responsible for product definition, performance projections, and modeling. He designed the I/O bus for the geometry chip described in the article. He came to HP in 1981 after receiving a BS degree in computer engineering from the University of Kansas. Daniel M. Olsen A software engineer in the graphics products laboratory at the HP Workstation Systems Division, Daniel Olsen is responsible for the development of new 3D products for HP workstations. He has been with HP since 1994. He has a BSEE degree (1991) from North Dakota State University and an MS degree in computer engineering (1997) from Iowa State University. Daniel was born in Des Moines, Iowa, is married and has two daughters. His leisure time activities include skiing, home projects, scuba diving, and aviation. Ethan W. Gannett Ethan Gannett is a lead engineer for graphics software development at the HP Workstation Systems Division. He came to HP in 1988 after receiving an MS degree in computer science from Iowa State University. He also holds a BS degree in physics (1983) and a BS degree in astronomy (1983) from the University of Iowa. Born in Davenport, Iowa, he is married and has one daughter. He enjoys kayaking, backcountry camping, telemarking, and hiking. " Go to Next Article " Go to Journal Home Page Article 4 • © 1998 Hewlett Packard Company 34 May 1998 • The Hewlett-Packard Journal