Intel D848PMB Product Specification Update - Page 13

Documentation Changes

|

View all Intel D848PMB manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 13 highlights

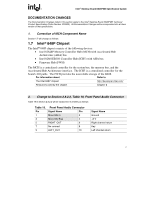

Intel® Desktop Board D848PMB Specification Update DOCUMENTATION CHANGES The Documentation Changes listed in this section apply to the Intel ®Desktop Board D848PMB Technical Product Specification (Order Number C53953). All Documentation Changes will be incorporated into a future version of that specification. 1. Correction of MCH Component Name Section 1.7 will change as follows: 1.7 Intel® 848P Chipset The Intel® 848P chipset consists of the following devices: • Intel 82848P Memory Controller Hub (MCH) with Accelerated Hub Architecture (AHA) bus • Intel 82801EB I/O Controller Hub (ICH5) with AHA bus • Firmware Hub (FWH) The MCH is a centralized controller for the system bus, the memory bus, and the Accelerated Hub Architecture interface. The ICH5 is a centralized controller for the board's I/O paths. The FWH provides the nonvolatile storage of the BIOS. For information about Refer to The Intel 848P chipset http://developer.intel.com/ Resources used by the chipset Chapter 2 2. Change to Section 2.8.2.2, Table 19, Front Panel Audio Connector Table 19 in Section 2.8.2.2 will be replaced in its entirety as follows: Table 19. Front Panel Audio Connector Pin Signal Name Pin 1 Mono Mic in 2 3 Mono Mic Bias 4 5 RIGHT_OUT 6 7 No connect 8 9 LEFT_OUT 10 Signal Name Ground +5 V Right channel return Key Left channel return 7