Intel DG965PZ Product Specification - Page 7

Regulatory Compliance and Battery Disposal Information, s, Tables

|

View all Intel DG965PZ manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 7 highlights

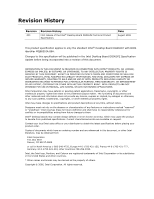

Contents 5 Regulatory Compliance and Battery Disposal Information 5.1 Regulatory Compliance 81 5.1.1 Safety Regulations 81 5.1.2 European Union Declaration of Conformity Statement 82 5.1.3 Product Ecology Statements 84 5.1.4 EMC Regulations 87 5.1.5 Product Certification Markings (Board Level 88 5.2 Battery Disposal Information 89 Figures 1. Major Board Components 12 2. Block Diagram 14 3. Memory Channel Configuration and DIMM Configuration 18 4. Dual Channel (Interleaved) Mode Configuration with Two DIMMs 19 5. Dual Channel (Interleaved) Mode Configuration with Three DIMMs ......... 19 6. Dual Channel (Interleaved) Mode Configuration with Four DIMMs 20 7. Single Channel (Asymmetric) Mode Configuration with One DIMM .......... 21 8. Single Channel (Asymmetric) Mode Configuration with Three DIMMs....... 21 9. Flex Mode Configuration with Two DIMMs 22 10. Front/Back Panel Audio Connector Options 29 11. LAN Connector LED Locations 31 12. Thermal Sensors and Fan Headers 33 13. Location of the Standby Power Indicator LED 40 14. Detailed System Memory Address Map 42 15. Back Panel Connectors 49 16. Component-side Connectors and Headers 50 17. Connection Diagram for Front Panel Header 55 18. Connection Diagram for Front Panel USB Headers 57 19. Connection Diagram for IEEE 1394a Header 57 20. Location of the Jumper Block 58 21. Board Dimensions 59 22. I/O Shield Dimensions 60 23. Localized High Temperature Zones 64 Tables 1. Feature Summary 10 2. Manufacturing Options 11 3. Board Components Shown in Figure 1 13 4. Supported Memory Configurations 16 5. Memory Operating Frequencies 17 6. DVI Port Status Conditions 25 7. Audio Jack Retasking Support 28 8. LAN Connector LED States 31 9. Effects of Pressing the Power Switch 34 10. Power States and Targeted System Power 35 vii