Intel P4304BT Technical Product Specification - Page 38

Serial ATA Support - drivers

|

View all Intel P4304BT manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 38 highlights

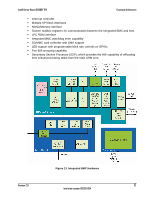

Functional Architecture Intel® Server Board S1200BT TPS One PCI-E x16 Gen3 connector to be used as a x8 link, two PCI-E x8 Gen3 connectors to be used as a x4 link and one SAS module Gen3 connector to be used as a x4 link connected to the PCI-E ports of the processor. One PCI-E x8 Gen2 connector to be used as x4 link connected to the PC-E ports of PCH. With Intel® Xeon® E3-1200 Processors or the 2nd Generation Intel® Core™ i3 Processors on S1200BTS o One PCI-E x16 Gen2 connector to be used as x8 link, one PCI-E x8 Gen2 connectors to be used as a x8 link connected to the PCI-E ports of the processor. One PCI-E x8 Gen2 connector to be used as x4 link connected to the PCI-E ports of PCH. With Intel® Xeon® E3-1200 V2 Processors or the 3rd Generation Intel® Core™ i3 Processors on S1200BTS o One PCI-E x16 Gen3 connector to be used as x8 link, one PCI-E x8 Gen3 connectors to be used as a x8 link connected to the PCI-E ports of the processor. One PCI-E x8 Gen2 connector to be used as x4 link connected to the PCI-E ports of PCH. There is one 32-bit, 33-MHz 5-V PCI slot, common on both SKUs. Compatibility with the PCI addressing model is maintained to ensure all existing applications and drivers operate unchanged. The PCI Express* configuration uses standard mechanisms as defined in the PCI Plug-andPlay specification. The initial recovered clock speed of 1.25 GHz results in 2.5 Gb/s each direction, which provides a 250-MB/s communications channel in each direction (500 MB/s total). This is close to twice the data rate of classic PCI. It is a fact that 8b/10b encoding is used accounts for the 250 MB/s where quick calculations would imply 300 MB/s. The external graphics ports support 5.0 GT/s speed as well. Operating at 5.0 GT/s results in twice as much bandwidth per lane as compared to 2.5 GT/s operation. When operating with two PCI Express* controllers, each controller can operate at either 2.5 GT/s or 5.0 GT/s. The PCI Express* architecture is specified in three layers: Transaction Layer, Data Link Layer, and Physical Layer. The partitioning in the component is not necessarily along these same boundaries. 3.4.3 Serial ATA Support The Intel® C200 Series chipset has two integrated SATA host controllers that support independent DMA operation on up to six ports and supports data transfer rates of up to 6.0 Gb/s on up to two ports (Port 0 and 1 Only on S1200BTL) while all ports support rates up to 3.0 Gb/s. The SATA controller contains two modes of operation - a legacy mode using I/O space, and an AHCI mode using memory space. Software that uses legacy mode will not have AHCI capabilities. Software that uses legacy mode does not have Advanced Host Configuration Interface (AHCI) capabilities. The Intel® C202 PCH Chipset supports the Serial ATA Specification, Revision 1.0a. The PCH also supports several optional sections of the Serial ATA II: Extensions to Serial ATA 1.0 Specification, Revision 1.0 (AHCI support is required for some elements). The Intel® C200 Series chipset PCH provides hardware support for AHCI, a standardized programming interface for SATA host controllers. Platforms supporting AHCI may take advantage of performance features such as no master/slave designation for SATA devices- 26 Revision 2.0 Intel order number G13326-004