Intel X6800 Specification Update - Page 25

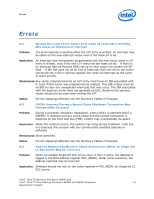

Pending x87 FPU Exceptions #MF Following STI May Be Serviced

|

UPC - 735858184663

View all Intel X6800 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 25 highlights

Errata Workaround: Use the IRET instruction to return from a system call, if RF flag has to be set after the return. Status: For the steppings affected, see the Summary Tables of Changes. AI7. General Protection Fault (#GP) for Instructions Greater than 15 Bytes May be Preempted Problem: When the processor encounters an instruction that is greater than 15 bytes in length, a #GP is signaled when the instruction is decoded. Under some circumstances, the #GP fault may be preempted by another lower priority fault (e.g. Page Fault (#PF)). However, if the preempting lower priority faults are resolved by the operating system and the instruction retried, a #GP fault will occur. Implication: Software may observe a lower-priority fault occurring before or in lieu of a #GP fault. Instructions of greater than 15 bytes in length can only occur if redundant prefixes are placed before the instruction. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. AI8. Pending x87 FPU Exceptions (#MF) Following STI May Be Serviced Before Higher Priority Interrupts Problem: Interrupts that are pending prior to the execution of the STI (Set Interrupt Flag) instruction are normally serviced immediately after the instruction following the STI. An exception to this is if the following instruction triggers a #MF. In this situation, the interrupt should be serviced before the #MF. Because of this erratum, if following STI, an instruction that triggers a #MF is executed while STPCLK#, Enhanced Intel SpeedStep Technology transitions or Thermal Monitor events occur, the pending #MF may be serviced before higher priority interrupts. Implication: Software may observe #MF being serviced before higher priority interrupts. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. AI9. The Processor May Report a #TS Instead of a #GP Fault Problem: A jump to a busy TSS (Task-State Segment) may cause a #TS (invalid TSS exception) instead of a #GP fault (general protection exception). Implication: Operation systems that access a busy TSS may get invalid TSS fault instead of a #GP fault. Intel has not observed this erratum with any commercially available software. Workaround: None Identified. Status: For the steppings affected, see the Summary Tables of Changes. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 25 Specification Update