Lenovo NetVista A40p Technical information manual for NetVista 6269, 6568, 656 - Page 45

Signal name, Signal, Table 21. System memory connector pin input/output, Table 20. System, memory

|

View all Lenovo NetVista A40p manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 45 highlights

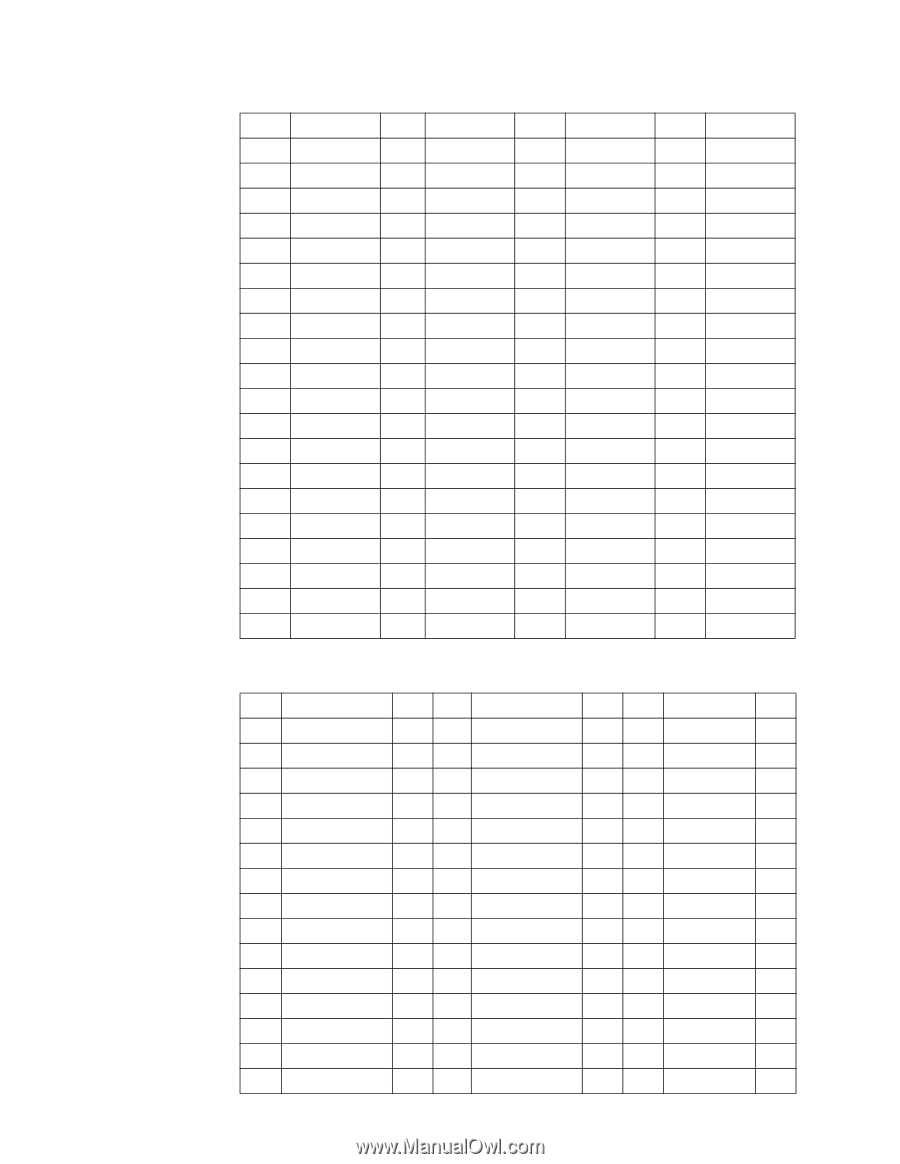

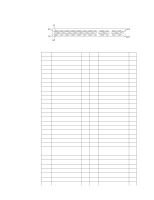

Table 20. System memory connector-pin assignments Pin Signal Pin Signal Pin Signal 23 VSS 24 NC 65 DQ21 66 DQ22 107 VSS 108 NC 25 NC 67 DQ23 109 NC 26 VCC 68 VSS 110 VCC 27 /WE 28 DQMB0 69 DQ24 70 DQ25 111 /CAS 112 DQMB4 29 DQMB1 71 DQ26 113 DQMB5 30 /S0 72 DQ27 114 NC 31 DU 73 VCC 115 /RAS 32 VSS 33 A0 74 DQ28 75 DQ29 116 VSS 117 A1 34 A2 76 DQ30 118 A3 35 A4 77 DQ31 119 A5 36 A6 37 A8 78 VSS 79 CK2 120 A7 121 A9 38 A10/AP 80 NC 122 BA0 39 NC 81 NC 123 NC 40 VCC 82 SDA 124 VCC 41 VCC 42 CK0 83 SCL 84 VCC 125 CK1 126 A12 Pin 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 Signal DQ53 DQ54 DQ55 VSS DQ56 DQ57 DQ58 DQ59 VCC DQ60 DQ61 DQ62 DQ63 VSS CK3 NC SA0 SA1 SA2 VCC Table 21. System memory connector pin input/output Pin Signal name I/O Pin Signal name 1 Ground N/A 57 MD18 2 MD0 I/O 58 MD19 3 MD1 4 MD2 I/O 59 VDD I/O 60 MD20 5 MD3 I/O 61 CKE1 6 VDD I/O 62 VREF 7 MD4 I/O 63 (CKE1)* 8 MD5 9 MD6 I/O 64 Ground I/O 65 MD21 10 MD7 I/O 66 MD22 11 MD8 (PAR0) I/O 67 MD23 12 Ground 13 MD9 N/A 68 I/O 69 Ground MD24 14 MD10 I/O 70 MD25 15 MD11 I/O 71 MD26 I/O Pin Signal name I/O I/O 113 DQMB4# I I/O 114 S1# I N/A 115 RAS# I I/O 116 Ground N/A N/A 117 A1 I N/A 118 A3 I N/A 119 A5 I N/A 120 A7 I I/O 121 A9 I I/O 122 A11 I I/O 123 NC N/A 124 VDD N/A I/O 125 CK1 N/A I/O 126 A14 O I/O 127 Ground N/A Appendix A. Connector-pin assignments 35