Sharp XL-HP737 Service Manual - Page 52

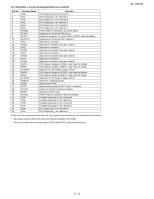

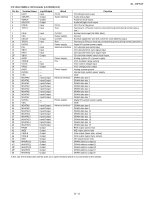

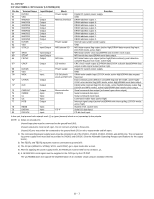

IC3 VHiLC78683E-1: MP3 Decoder LC78683E 2/2, Pin No., Terminal Name, Input/Output, Block, Function

|

View all Sharp XL-HP737 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 52 highlights

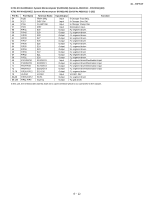

XL-HP737 IC3 VHiLC78683E-1: MP3 Decoder (LC78683E) (2/2) Pin No. 51 52 53 54 55 56 57 58 59 60 61 62 63* Terminal Name DVDD4 VSS MADRS7 MADRS6 MADRS5 MADRS4 MADRS3 MADRS2 MADRS1 MADRS0 DVDD5 VSS STREQ 64* STCK 65* STDAT 66 FSYNC 67* CRCF 68 DVDD6 69 VSS 70* WOK 71* CNTOK 72* OVF 73 CMDOUT 74 CMDIN 75 CL 76 CE 77 INTB 78 RESB 79 DATAIN 80 DATACK Input/Output - - Output Output Output Output Output Output Output Output - - Input/Output Input/Output Input/Output Output Output - - Input Output Output Output Input Input Input Output Input Input Input Block Power supply Memory interface Power supply MP3 stream I/O MP3-dec CD monitor Power supply CD-DA shockproof and MP3 I/O Microcontroller interface CD IF Function Digital I/O system power supply. GND DRAM address output 7. DRAM address output 6. DRAM address output 5. DRAM address output 4. DRAM address output 3. DRAM address output 2. DRAM address output 1. DRAM address output 0. Internal logic system power supply. GND MP3 data request flag output.(active high)/DRAM data request flag input. (CD-ROM mode, active high) MP3 data transfer clock input/DRAM data transfer clock output. MP3 serial data input/DRAM serial data output. MP3 data frame sync signal (active high)/Data continuity point detection complete flag.(CD-DA mode, active high) CRC check result output (CD-ROM data/CD-DA subcode data)/DRAM data output enable signal output.(active high) Digital I/O system power supply. GND DRAM write enable input (CD-DA mode, active high)/DRAM data request flag input. Data continuity point detection complete flag (CD-DA mode, active high)/ SYNC error monitor flag (MP3 mode, active high)/DRAM serial data output. DRAM write interrupt flag (CD-DA mode, active high)/Emphasis output flag (CD-DA and MP3 modes, active high)/DRAM data transfer clock output. Serial command data output.(n-channel open-drain output) Serial command data input. Serial command clock input. Command enable input (active high) Interrupt signal output (active low)/DRAM write interrupt flag. (CD-DA mode, active high) System reset. (active low) Serial CD data input. CD bit clock input. In this unit, the terminal with asterisk mark (*) is (open) terminal which is not connected to the outside. NOTE: 1) Notes on unused pins Unused input pins must be connected to the ground level (0V). Unused output pins must be left open. Do not connect anything to these pins. Unused I/O pins may either be connected to the ground level (0V) or set to output mode and left open. 2) The corresponding power supply levels must be provided to all of the DVDD1, DVDD3, DVDD4, DVDD6, and AVDD pins. The corresponding power supply level must also be provided to DVDD2 and DVDD5. (See the Allowable Operating Ranges specifications for the supply levels.) 3) The TEST1 and TEST2 input pins must be connected to ground (0V). 4) The I/O pins (MDA0:15, STREQ, STCK, and STDAT) go to input mode after a reset. 5) After fist applying the power supply levels, the RESB pin must be held low for at least 1 µs. 6) A 16.9344 MHz clock signal must be supplied to the CKIN pin by the CD DSP. The LC786484E does not support the implementation of an oscillator circuit using an oscillator element. 8 - 7