Gigabyte GA-790XTA-UD4 Manual - Page 40

CPU Host Clock Control, CPU Frequency MHz, Set Memory Clock, DCTs Mode, DDR3 Timing Items, MB

|

UPC - 818313009364

View all Gigabyte GA-790XTA-UD4 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 40 highlights

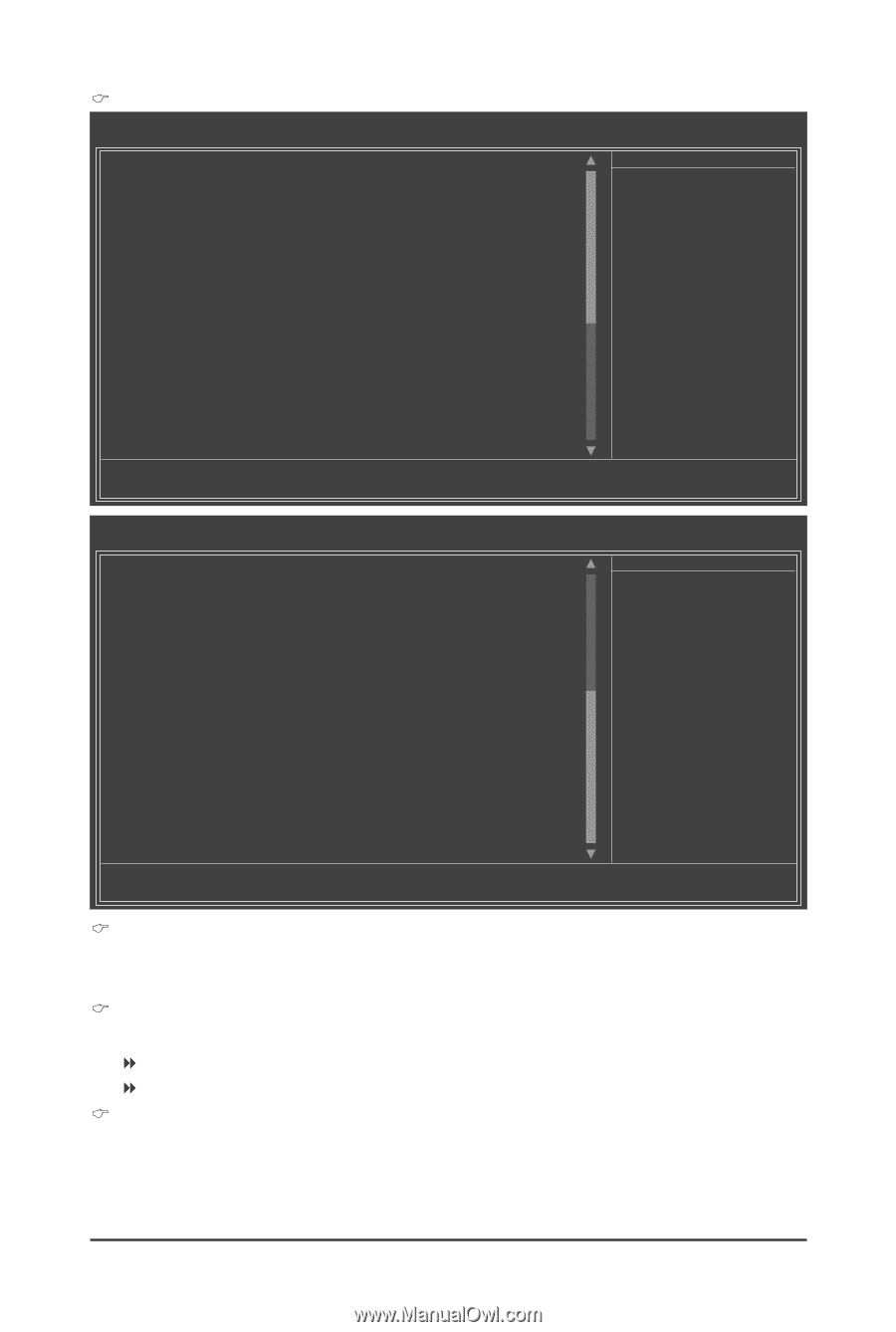

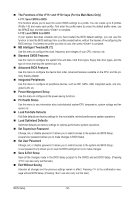

DRAM Configuration CMOS Setup Utility-Copyright (C) 1984-2009 Award Software DRAM Configuration CPU Host Clock Control x CPU Frequency(MHz) Set Memory Clock x Memory Clock DCTs Mode DDR3 Timing Items x CAS# latency x RAS to CAS R/W Delay x Row Precharge Time x Minimum RAS Active Time x 1T/2T Command Timing x TwTr Command Delay x Trfc0 for DIMM1 x Trfc2 for DIMM2 x Trfc1 for DIMM3 x Trfc3 for DIMM4 x Write Recovery Time x Precharge Time x Row Cycle Time [Auto] 200 [Auto] x6.66 [Unganged] [Auto] Auto Auto Auto Auto Auto Auto Auto Auto Auto Auto Auto Auto Auto 1333Mhz SPD 9T 9T 9T 24T -5T 110ns ---10T 5T 33T Auto 9T 9T 9T 24T -5T 110ns ---10T 5T 33T Item Help Menu Level Move Enter: Select F5: Previous Values +/-/PU/PD: Value F10: Save F6: Fail-Safe Defaults ESC: Exit F1: General Help F7: Optimized Defaults CMOS Setup Utility-Copyright (C) 1984-2009 Award Software DRAM Configuration x RAS to RAS Delay CHA ProcOdt CHA DQS drive strength CHA Data drive strength CHA MEMCLK drive strength CHA Add/Cmd drive strength CHA CS/ODT drive strength CHA CKE drive strength CHB ProcOdt CHB DQS drive strength CHB Data drive strength CHB MEMCLK drive strength CHB Add/Cmd drive strength CHB CS/ODT drive strength CHB CKE drive strength Bank Interleaving Channel interleave Auto [Auto] [Auto] [Auto] [Auto] [Auto] [Auto] [Auto] [Auto] [Auto] [Auto] [Auto] [Auto] [Auto] [Auto] [Enabled] [Enabled] 4T 4T 60 ohms 1.0x 1.0x 1.25x 1.5x 1.5x 1.5x 60 ohms 1.0x 1.0x 1.25x 1.5x 1.5x 1.5x Item Help Menu Level Move Enter: Select F5: Previous Values +/-/PU/PD: Value F10: Save F6: Fail-Safe Defaults ESC: Exit F1: General Help F7: Optimized Defaults CPU Host Clock Control, CPU Frequency (MHz), Set Memory Clock, Memory Clock The settings under the four items above are synchronous to those under the same items on the MB Intelligent Tweaker(M.I.T.) main menu. DCTs Mode Allows you to set memory control mode. Ganged Sets memory control mode to single dual-channel. Unganged Sets memory control mode to two single-channel. (Default) DDR3 Timing Items Manual allows all DDR3 Timing items below to be configurable. Options are: Auto (default), Manual. BIOS Setup - 40 -