Gigabyte GA-880GA-UD3H Manual - Page 40

DCTs Mode, DDR3 Timing Items, CAS# latency, RAS to CAS R/W Delay, Options are: Auto default, 4T~12T.

|

UPC - 818313010353

View all Gigabyte GA-880GA-UD3H manuals

Add to My Manuals

Save this manual to your list of manuals |

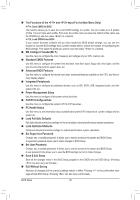

Page 40 highlights

DRAM Configuration CMOS Setup Utility-Copyright (C) 1984-2010 Award Software DRAM Configuration DCTs Mode DDR3 Timing Items x CAS# latency x RAS to CAS R/W Delay x Row Precharge Time x Minimum RAS Active Time x 1T/2T Command Timing x TwTr Command Delay x Trfc0 for DIMM1 x Trfc2 for DIMM2 x Trfc1 for DIMM3 x Trfc3 for DIMM4 x Write Recovery Time x Precharge Time x Row Cycle Time x RAS to RAS Delay **DCTs Drive Strength** ProcOdt(ohms) DQS Drive Strength [Unganged] [Auto] SPD Auto Auto 9T 9T Auto 9T 9T Auto 9T 9T Auto 24T 24T Auto -- -- Auto 5T 5T Auto 110ns 110ns Auto -- -- Auto -- -- Auto -- -- Auto 10T 10T Auto 5T 5T Auto 33T 33T Auto 4T 4T DCT0 DCT1 [Auto] 60 [Auto] 240 [Auto] 1.0x [Auto] 1.5x Item Help Menu Level Move Enter: Select F5: Previous Values +/-/PU/PD: Value F10: Save F6: Fail-Safe Defaults ESC: Exit F1: General Help F7: Optimized Defaults CMOS Setup Utility-Copyright (C) 1984-2010 Award Software DRAM Configuration Data Drive Strength MEMCLK Drive Strength Addr/Cmd Drive Strength CS/ODT Drive Strength CKE Drive Strength [Auto] 1.0x [Auto] 1.5x [Auto] 1.5x [Auto] 1.5x [Auto] 1.5x [Auto] 2.0x [Auto] 1.5x [Auto] 2.0x [Auto] 1.5x [Auto] 2.0x Item Help Menu Level Bank Interleaving Channel Interleave [Enabled] [Enabled] Move Enter: Select F5: Previous Values +/-/PU/PD: Value F10: Save F6: Fail-Safe Defaults ESC: Exit F1: General Help F7: Optimized Defaults DCTs Mode Allows you to set memory control mode. Ganged Sets memory control mode to single dual-channel. Unganged Sets memory control mode to two single-channel. (Default) DDR3 Timing Items Manual allows all DDR3 Timing items below to be configurable. Options are: Auto (default), Manual. CAS# latency Options are: Auto (default), 4T~12T. RAS to CAS R/W Delay Options are: Auto (default), 5T~12T. BIOS Setup - 40 -