HP BL680c HP local I/O technology for ProLiant and BladeSystem servers - Page 3

PCI Express technology, Gigabyte/second link, designated x4 pronounced by four.

|

UPC - 884420396314

View all HP BL680c manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 3 highlights

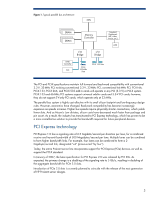

Figure 1. Typical parallel bus architecture CPU DRAM DRAM Memory Controller Standard Peripherals (KB, video, mouse, etc.) iLO I/O Bridge I/O Bridge RAID Controller NIC PCI-X 100-MHz Slots PCI-X 133 Slots The PCI and PCI-X specifications maintain full forward and backward compatibility with conventional 3.3-V, 33-MHz PCI; existing conventional 3.3-V, 33-MHz PCI, conventional 66-MHz PCI, PCI-X 66, PCI-X 133, PCI-X 266, and PCI-X 533 add-in cards will operate in any PCI (3.3 V) or PCI-X system. PCI-X 133 and 66-MHz PCI systems support universal add-in cards and 3.3-V PCI cards; however, they do not support 5-V-only PCI cards, which operate only at 33 MHz. The parallel bus system is highly cost effective with its small silicon footprint and low-frequency design rules. However, economics have changed. Backward compatibility has become increasingly expensive as speeds increase. Higher bus speeds require physically shorter connections, which yields fewer slots. And as Moore's Law dictates, silicon costs have decreased much faster than package and pin count. As a result, the industry has transitioned to PCI Express technology, which has proven to be a more cost-effective solution to provide the bandwidth required for future peripheral devices. PCI Express technology PCI Express 1.0 has a signaling rate of 2.5 Gigabits/second per direction per lane, for a combined receive and transmit bandwidth of 500 Megabytes/second per lane. Multiple lanes can be combined to form higher bandwidth links. For example, four lanes can be combined to form a 2Gigabyte/second link, designated "x4" (pronounced "by four"). Today, the entire ProLiant server line incorporates support for PCI Express (PCIe) devices, as well as support the PCI-X standard. In January of 2007, the base specification for PCI Express 2.0 was released by PCI SIG. As expected, the primary change is a doubling of the signaling rate to 5 Gb/s, resulting in doubling of the aggregate bandwidth for PCIe 2.0 slots. Introduction of PCIe 2.0 slots is currently planned to coincide with the release of the next generation of HP ProLiant server designs. 3