HP BL680c HP local I/O technology for ProLiant and BladeSystem servers - Page 5

b/10b encoding, Performance, TX FIFO, Transmit TX, Receive RX

|

UPC - 884420396314

View all HP BL680c manuals

Add to My Manuals

Save this manual to your list of manuals |

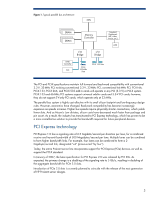

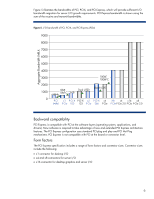

Page 5 highlights

8b/10b encoding Serial communication requires a device to convert parallel data into a serial bit stream and vice versa. This device, called a serializer/deserializer (SerDes), contains a parallel digital interface, First-In-First-Out (FIFO) caches, 8 bit/10 bit (8b/10b) encoder and decoder, a parallel-to-serial converter, and a serial-to-parallel converter (Figure 4). The 8b/10b encoder converts each 8-bit data byte to a 10-bit transmission symbol, which enables clocking information to be encoded into the data stream. Although this adds about 20 percent overhead to the data stream, it is the most common data signaling method when the signaling rates exceed 1 GHz. Figure 4. The SerDes core integrates 8b/10b coding and decoding logic. Transmit (TX) 8-bit parallel interface Receive (RX) SerDes (serializer/deserializer) core TX FIFO 8b/10b encoder parallel-to- serial TX converter RX FIFO 8b/10b decoder serial-toparallel RX converter LVD signaling +_ out 10-bit serial data + _ in Performance As previously mentioned, each PCI Express link's bandwidth can be linearly scaled by increasing the number of lanes. PCI Express Gen1 has a signaling rate of 2.5 Gb/s per lane in each direction, resulting in a unidirectional bandwidth of 250 MB/s after accounting for 8b/10b encoding overhead. Combining eight lanes provides a total unidirectional bandwidth of 2 GB/s, which would be sufficient to support the full wire speed of 10-Gb/s technologies such as 10-Gb Ethernet (about 1.25 GB/s, unidirectionally). PCI Express 2.0 increases the signaling rate from 2.5 Gb/s to 5 Gb/s, giving it a unidirectional bandwidth of 500 MB/s per lane (after factoring encoding overhead). With this bandwidth, the PCI Express 2.0 x4 link will support a 10-Gb Ethernet device, and a x8 link will support the high-speed server I/O peripherals that are expected to exist through the end of the decade. PCI-SIG is currently researching and defining specifications for a PCI Express 3.0 architecture. PCI Express 3.0 will support a bit rate of 8 GT/s (Giga Transactions per second). The 8 GT/s bit rate represents a net doubling of the delivered bandwidth of PCIe 2.0 and is achieved using increased signaling speed and by removing the requirement for the 8b/10b encoding scheme used in prior versions of the PCIe architecture, which imposed a 20 percent overhead on the raw bit rate. 5