Intel SL6VU Specification Update

Intel SL6VU - Celeron 2.40GHz 400MHz 128KB Socket 478 CPU Manual

|

UPC - 683728093976

View all Intel SL6VU manuals

Add to My Manuals

Save this manual to your list of manuals |

Intel SL6VU manual content summary:

- Intel SL6VU | Specification Update - Page 1

in the 478-Pin Package Specification Update October 2006 Notice: The Intel® Celeron® Processor in the 478-Pin Package may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current - Intel SL6VU | Specification Update - Page 2

or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The Intel® Celeron® Processor in the 478-Pin Package may - Intel SL6VU | Specification Update - Page 3

History ...4 Preface ...6 Summary Tables of Changes 8 General Information ...14 Component Identification Information 15 Errata...19 Specification Changes ...46 Specification Clarifications 47 Documentation Changes 50 § Intel® Celeron® Processor in the 478-Pin Package Specification Update 3 - Intel SL6VU | Specification Update - Page 4

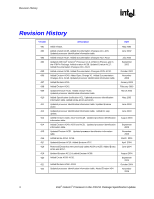

- AC12. Updated with Intel® Celeron® Processor on 0.13 Micron Process and in the 478-Pin Package. Added erratum AC38. Updated Erratum AC17. Added Documentation Changes AC3- AC24. Added erratum AC39. Added Documentation Changes AC25- AC32. Added Erratum AC40. Added Spec Change V1. Added Documentation - Intel SL6VU | Specification Update - Page 5

Table of Changes. • Updated the names of the Software Developer Manuals. Updated Summary Table of Changes. Updated Links. Date December 2004 April 2005 October 2005 January 2006 March 2006 April 2006 June 2006 October 2006 Intel® Celeron® Processor in the 478-Pin Package Specification Update 5 - Intel SL6VU | Specification Update - Page 6

http://developer.intel.com/support /processors/celeron/478/ Related Documents Document Title Intel® 64 and IA-32 Intel® Architectures Software Developer's Manual, Volume 1: Basic Architecture Intel® 64 and IA-32 Intel® Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference - Intel SL6VU | Specification Update - Page 7

characteristics (e.g., core speed, L2 cache size, package type, etc.) as described in the processor identification information table. Care should be taken to read all notes associated with each S-Spec number Errata are design defects or errors. Errata may cause the Intel® Celeron® processor in the - Intel SL6VU | Specification Update - Page 8

, or Documentation Changes that apply to the listed component steppings. Intel intends to fix some of the errata in a future stepping are no plans to fix this erratum. This column refers to errata on the Celeron processor in the 478-pin package substrate APIC related erratum. Shaded: This item is - Intel SL6VU | Specification Update - Page 9

4 processor supporting Hyper-Threading Technology on 90- nm process technology R = Intel® Pentium® 4 processor on 90 nm process S = 64-bit Intel® Xeon™ processor with 800 MHz system bus (1 MB and 2 MB L2 cache versions) T = Mobile Intel® Pentium® 4 processor-M V = Mobile Intel® Celeron® processor on - Intel SL6VU | Specification Update - Page 10

byte X NoFix FSW may not be completely restored after page fault on FRSTOR or FLDENV instructions X NoFix The processor flags #PF instead of #AC on an unlocked CMPXCHG8B instruction Processor issues inconsistent transaction size attributes for locked operation 10 Intel® Celeron® Processor - Intel SL6VU | Specification Update - Page 11

L2 cache line and ECC error combination may result in loss of cache coherency Processor may hang when resuming from Deep Sleep state When the processor do not Fence Pending Instruction Page Walks Processor Provides a 4-Byte Store Unlock After an 8-Byte Load Lock Intel® Celeron® Processor in the 478- - Intel SL6VU | Specification Update - Page 12

NoFix Control Register 2 (CR2) Can be Updated during a REP MOVS/STOS Instruction with Fast Strings Enabled X NoFix Writing the Local Vector Table (LVT) when a Cache Line X NoFix without Proper Semaphores or Barriers May Expose a Memory Ordering Issue 12 Intel® Celeron® Processor in the - Intel SL6VU | Specification Update - Page 13

for this Month NO. E0 nC1 nD1 SPECIFICATION CLARIFICATIONS No Update for this month. NO. E0 nC1 nD1 DOCUMENTATION CHANGES Refer to Documentation Changes section § Intel® Celeron® Processor in the 478-Pin Package Specification Update 13 - Intel SL6VU | Specification Update - Page 14

and/or in the 478-Pin Package S-Spec/Country of Assy FPO -- 2-D Matrix Mark i m © '03 2ACeGleHrZo/n5®12/400/1.50V S2YGYHYZY/1X2X8X/4X0X0X FSFYFYFYFYFFXFX-XNXNXNXN iFFmFF©FF'0F1F - ATPO LOT N NNNN § Frequency/Cache/Bus 14 Intel® Celeron® Processor in the 478-Pin Package Specification Update - Intel SL6VU | Specification Update - Page 15

the EBX register after the CPUID instruction is executed with a 1 in the EAX register. Table 1. Intel® Celeron® Processor in the 478-Pin Package Processor Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Speed Core/Bus Package and Revision SL69Z E0 - Intel SL6VU | Specification Update - Page 16

Component Identification Information R Table 1. Intel® Celeron® Processor in the 478-Pin Package Processor Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Speed Core/Bus Package and Revision SL6RV C1 SL6VR D1 SL6VY D1 SL6RT C1 SL6RS C1 - Intel SL6VU | Specification Update - Page 17

1. Intel® Celeron® Processor in the 478-Pin Package Processor Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Speed Core/Bus Package and Revision SL6W2 D1 SL6XJ C1 SL6WC D1 SL6WD D1 SL6T2 C1 SL6T5 C1 SL6VU C1 SL6W4 D1 SL6XG C1 SL6V2 - Intel SL6VU | Specification Update - Page 18

Component Identification Information R Table 1. Intel® Celeron® Processor in the 478-Pin Package Processor Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Speed Core/Bus Package and Revision SL6VV C1 SL77U D1 SL77S D1 SL77T D1 SL77V D1 - Intel SL6VU | Specification Update - Page 19

(MCE) Problem: If an I/O instruction (IN, INS, REP INS, OUT, OUTS, or REP OUTS) is being executed, and if the data for this instruction becomes corrupted, the processor will signal , see the Summary Tables of Changes. Intel® Celeron® Processor in the 478-Pin Package Specification Update 19 - Intel SL6VU | Specification Update - Page 20

same physical 64-byte cache line as any Byte Problem: Some invalid opcodes require a ModRM byte (or other following bytes), while others do not. The invalid opcode 0FFFh did not require a ModRM byte in previous generation Intel® architecture processors, but does in the Intel® Pentium® 4 processor - Intel SL6VU | Specification Update - Page 21

with the caching permitted by other memory types Implication: This erratum may result in some performance degradation when using no-fill mode with large pages. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. Intel® Celeron® Processor in the - Intel SL6VU | Specification Update - Page 22

the Summary Tables of Changes. AC11. IA32_MC0_STATUS Register Overflow Bit Not Set Correctly Problem: The Overflow Error bit (bit 62) in the IA32_MC0_STATUS register indicates, when , see the Summary Tables of Changes. 22 Intel® Celeron® Processor in the 478-Pin Package Specification Update - Intel SL6VU | Specification Update - Page 23

May Contain Incorrect Information for Correctable Errors Problem: When a speculative load operation hits the L2 cache and receives a correctable error, the steppings affected, see the Summary Tables of Changes. Intel® Celeron® Processor in the 478-Pin Package Specification Update 23 - Intel SL6VU | Specification Update - Page 24

As Expected Problem: Certain debug mechanisms may not function as expected on the processor. The cases are as follows: • When the following conditions occur: 1) An FLD instruction signals a stack overflow or underflow, 2) the FLD instruction splits a page-boundary or a 64-byte cache line boundary - Intel SL6VU | Specification Update - Page 25

IA32_MC2_STATUS register, are not logged. • When one half of a 64 byte instruction fetch from the L2 cache has an uncorrectable error and the other 32 byte half of the same fetch from the L2 cache has a correctable error, the processor will attempt to correct the correctable error but cannot proceed - Intel SL6VU | Specification Update - Page 26

Cascading of Performance Counters Does Not Work Correctly When Forced Overflow Is Enabled Problem: The performance counters are organized into pairs. When the CASCADE bit of the affected, see the Summary Tables of Changes. 26 Intel® Celeron® Processor in the 478-Pin Package Specification Update - Intel SL6VU | Specification Update - Page 27

are set to a duty cycle of 12.5% or 25%, the processor may hang while attempting to execute a floating-point instruction. In this failure, the last instruction pointer (LIP) is pointing to a floating-point instruction whose instruction bytes are in UC space and which takes an exception 16 (floating - Intel SL6VU | Specification Update - Page 28

computation prior to execution of a SQRTPD or SQRTSD instruction. Status: For the steppings affected, see the Summary Tables of Changes. AC23. Bus Invalidate Line Requests That Return Unexpected Data May Result in L1 Cache Corruption Problem: When a Bus Invalidate Line (BIL) request receives - Intel SL6VU | Specification Update - Page 29

Problem: Processor and Intel® 850 Chipset Platform Design Guide are not expected to be affected. Workaround: No workaround is necessary for systems with margin sufficient to accept a higher RON. Status: For the steppings affected, see the Summary Tables of Changes. Intel® Celeron® Processor - Intel SL6VU | Specification Update - Page 30

Error Combination May Result in Loss of Cache Coherency Problem: When a Read for Ownership (RFO) cycle has a 64-bit address match with an outstanding read hit on a line in the L2 cache which is in the S-state AND that line contains an ECC error, the processor should recycle the RFO until the ECC - Intel SL6VU | Specification Update - Page 31

When Using Event Selection Control (ESCR) MSR Problem: ESCR MSRs allow software to select specific -retirement events that support precise-event-based sampling (PEBS). A number of performance metrics that support PEBS require a Intel® Celeron® Processor in the 478-Pin Package Specification Update - Intel SL6VU | Specification Update - Page 32

LSS instruction but the value of CR2 and the error code pushed on the stack are reflective of the speculative state. Intel has -Invalidate Line (BRIL) Problem: A processor internal cache fatal data ECC error may cause the processor to issue a BWL transaction to the same cache line address as an - Intel SL6VU | Specification Update - Page 33

in the L2 cache. Implication: Stale data may be consumed leading to unpredictable program execution. Intel has not A20M# and INIT# May Result in Incorrect Data Fetch Problem: If A20M# and INIT# are simultaneously asserted by Intel® Celeron® Processor in the 478-Pin Package Specification Update - Intel SL6VU | Specification Update - Page 34

the store to the APIC register before any subsequent instructions are executed. No commercial operating system is known to be impacted by this erratum. Status: For the steppings affected, see the Summary Tables of Changes 34 Intel® Celeron® Processor in the 478-Pin Package Specification Update - Intel SL6VU | Specification Update - Page 35

Cause the Processor to Hang Problem: If a locked operation accesses a line in the L1 cache that has a parity error, it is possible that the processor may hang while trying to evict the line. Implication: If this erratum occurs, it may result in a system hang. Intel has not observed this erratum - Intel SL6VU | Specification Update - Page 36

the Resume Flag (RF Flag) in a Task-State Segment (TSS) May Be Incorrect Problem: After executing a JMP instruction to the next (or other) task through a hardware task switch, it is possible the Summary Tables of Changes. 36 Intel® Celeron® Processor in the 478-Pin Package Specification Update - Intel SL6VU | Specification Update - Page 37

Changes. AC48. Processor Provides a 4-Byte Store Unlock after an 8-Byte Load Lock Problem: When the processor is in the processor. Implication: The processor may hang. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes Intel® Celeron® Processor - Intel SL6VU | Specification Update - Page 38

breaks at the instruction breakpoint address instead of single stepping. Workaround: Execution after the break will continue, if you manually clear DR7 bit 1 (Global Breakpoint Enable). Status: For the steppings affected, see the Summary Tables of Changes. 38 Intel® Celeron® Processor in the - Intel SL6VU | Specification Update - Page 39

(#DB) May Occur When a Data Breakpoint Is Set on an FP Instruction Problem: The default Microcode Floating Point Event Handler routine executes a series of loads to steppings affected, see the Summary Tables of Changes. Intel® Celeron® Processor in the 478-Pin Package Specification Update 39 - Intel SL6VU | Specification Update - Page 40

, since the logical processor will not be able to service any pending event. This erratum has not been observed in any commercial platform running commercial software. Workaround: None Status: For the steppings affected, see the Summary Tables of Changes. 40 Intel® Celeron® Processor in the 478 - Intel SL6VU | Specification Update - Page 41

occur. Workaround: It is possible for the BIOS to contain a workaround for this erratum Status: For the steppings affected, see the Summary Tables of Changes. Intel® Celeron® Processor in the 478-Pin Package Specification Update 41 - Intel SL6VU | Specification Update - Page 42

Step Trap before Retirement of Instruction Problem: If an FP instruction generates an unmasked exception with sizes as recommended in the Programmers Reference Manual Volume 3. Status: For the steppings affected the cache line associated with (1) BWIL 42 Intel® Celeron® Processor in the - Intel SL6VU | Specification Update - Page 43

Instruction with Fast Strings Enabled Transaction Problem: Under limited circumstances while executing a REP MOVS/STOS string instruction vector will be left set in the in-service register and mask all interrupts at the same Intel® Celeron® Processor in the 478-Pin Package Specification Update 43 - Intel SL6VU | Specification Update - Page 44

Unaligned Data that Crosses a Cache Line without Proper Semaphores or Barriers May Expose a Memory Ordering Issue Problem: Software which is written or "POP SS" instruction is immediately followed by a hardware debugger breakpoint instruction, or 44 Intel® Celeron® Processor in the 478-Pin - Intel SL6VU | Specification Update - Page 45

this erratum the breakpoint condition detected flags may be set incorrectly. Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. Intel® Celeron® Processor in the 478-Pin Package Specification Update 45 - Intel SL6VU | Specification Update - Page 46

The Specification Changes listed in this section apply to the following documents: • Intel® Celeron® Processor in the 478-Pin Package Datasheet • Intel® 64 and IA-32 Intel® Architectures Software Developer's Manual, Volumes 1, 2-A, 2B, 3-A, and 3-B All Specification Changes will be incorporated into - Intel SL6VU | Specification Update - Page 47

Intel® Architecture Software Developer's Manual Volume 3: System Programming Guide, the Time Stamp Counter definition has been updated to include support for the future processors P6 family and Pentium processors) - The MSR used as the counter. • RDTSC instruction - An instruction used to read the - Intel SL6VU | Specification Update - Page 48

To determine average processor clock frequency, Intel recommends the use of Performance Monitoring logic to count processor core clocks over the period of time for which the average is required. See Section 15.10.9 and Appendix A in this manual for more information. The RDTSC instruction reads the - Intel SL6VU | Specification Update - Page 49

counter value can be read with the RDTSC instruction. The time-stamp counter and the non-sleep clockticks count may not agree in all cases and for all processors. See Section 10.8 for more information on counter operation. § Intel® Celeron® Processor in the 478-Pin Package Specification Update - Intel SL6VU | Specification Update - Page 50

The Documentation Changes listed in this section apply to the following documents: • Intel® Celeron® Processor in the 478-Pin Package Datasheet • Intel® 64 and IA-32 Intel® Architectures Software Developer's Manual, Volumes 1, 2-A, 2B, 3-A, and 3-B All Documentation Changes will be incorporated into

Intel

®

Celeron

®

Processor in the

478-Pin Package

Specification Update

October 2006

R

Notice:

The Intel

®

Celeron

®

Processor in the 478-Pin Package may contain design

defects or errors known as errata which may cause the product to deviate from

published specifications. Current characterized errata are documented in this

Specification Update.

Document Number: 290749-030