ASRock B85M-ITX User Manual - Page 62

DRAM Timing Configuration, Load XMP Setting, DRAM Frequency, DRAM Tweaker, CAS# Latency tCL

|

View all ASRock B85M-ITX manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 62 highlights

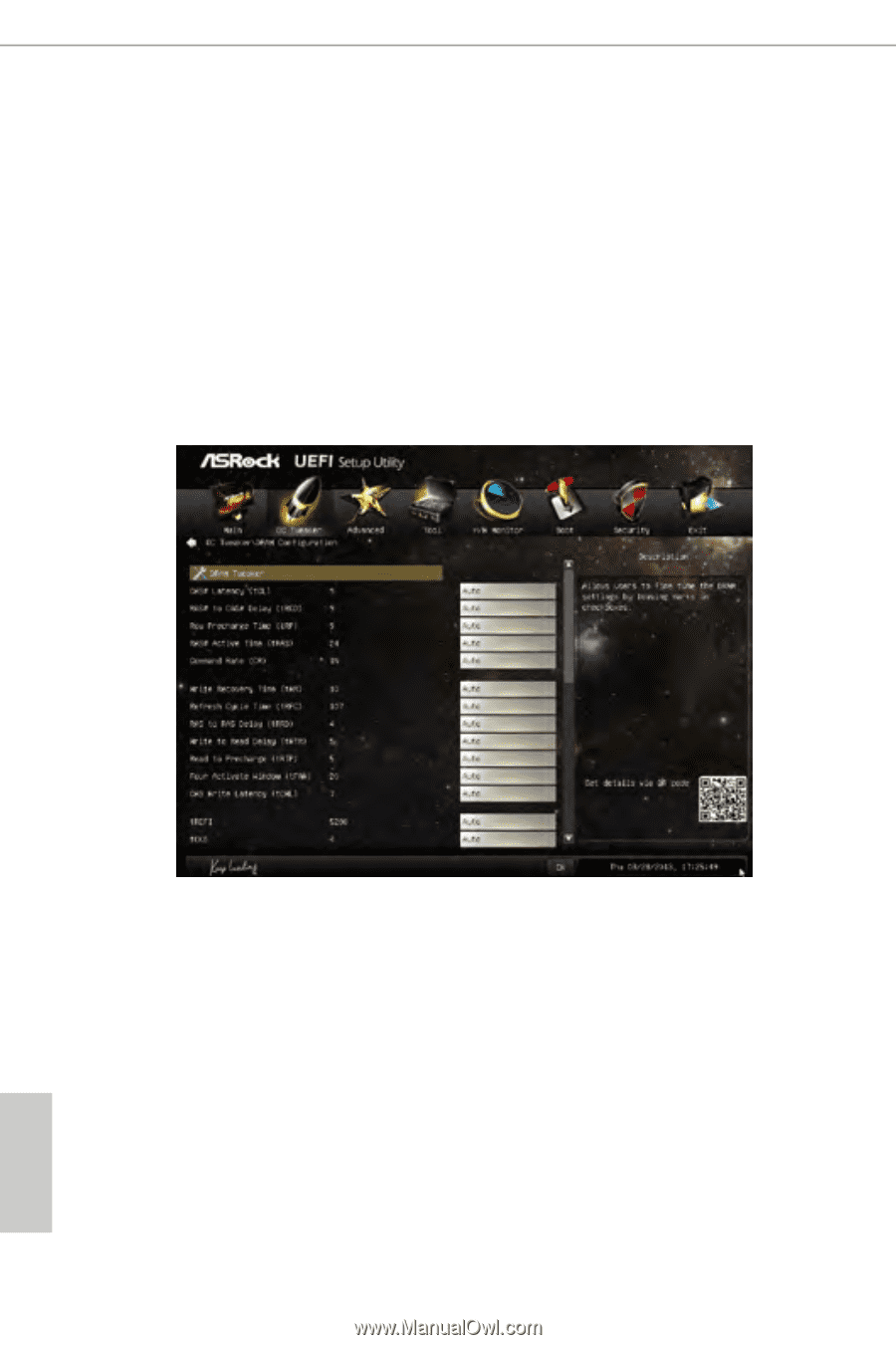

DRAM Timing Configuration Load XMP Setting Load XMP settings to overclock the DDR3 memory and perform beyond standard specifications. DRAM Frequency If [Auto] is selected, the motherboard will detect the memory module(s) inserted and assign the appropriate frequency automatically. DRAM Configuration DRAM Tweaker Fine tune the DRAM settings by leaving marks in checkboxes. Click OK to confirm and apply your new settings. CAS# Latency (tCL) The time between sending a column address to the memory and the beginning of the data in response. RAS# to CAS# Delay (tRCD) The number of clock cycles required between the opening of a row of memory and accessing columns within it. 58 English

58

English

DRAM Timing Configuration

Load XMP Setting

Load XMP settings to overclock the DDR3 memory and perform beyond standard

specifications.

DRAM Frequency

If [Auto] is selected, the motherboard will detect the memory module(s) inserted

and assign the appropriate frequency automatically.

DRAM Configuration

DRAM Tweaker

Fine tune the DRAM settings by leaving marks in checkboxes. Click OK to confirm and

apply your new settings.

CAS# Latency (tCL)

°e time between sending a column address to the memory and the beginning of the data

in response.

RAS# to CAS# Delay (tRCD)

°e number of clock cycles required between the opening of a row of memory and

accessing columns within it.