ASRock P5B-DE User Manual - Page 31

Dram Tcl, Dram Trcd, Dram Trp, Dram Tras, Dram Trfc, Dram Twr, Dram Trrd, Rcomp Control G0, Dram

|

View all ASRock P5B-DE manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 31 highlights

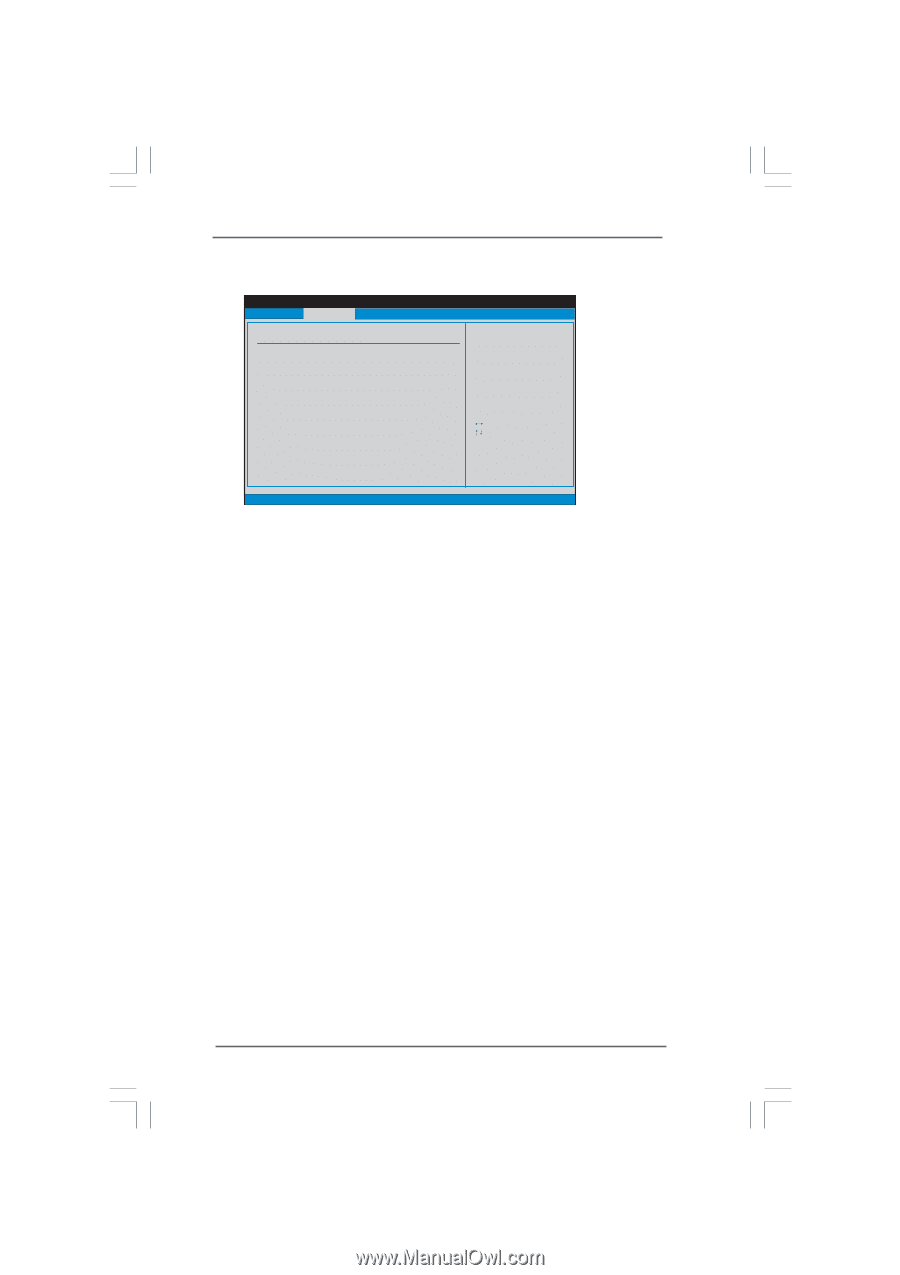

DRAM Timing Control BIOS SETUP UTILITY Advanced DRAM Timing Control Current Setting : 5-5-5-18-51-6-3 DRAM tCL [Auto] DRAM tRCD DRAM tRP DRAM tRAS [Auto] [Auto] [Auto] DRAM tRFC [Auto] DRAM tWR [Auto] DRAM tRRD [Auto] Current Setting : 66-66-33-33-88-88-66-45-24 Rcomp Control G0 [Auto] Rcomp Control G1 (CMD) [Auto] Rcomp Control G2 [Auto] Rcomp Control G3 [Auto] Rcomp Control G4 [Auto] Rcomp Control G5 Rcomp Control G6 [Auto] [Auto] DRAM tCL Min = 3 Max = 6 +F1 F9 F10 ESC Select Screen Select Item Change Option General Help Load Defaults Save and Exit Exit v02.54 (C) Copyright 1985-2005, American Megatrends, Inc. DRAM tCL This controls the number of DRAM clocks for TCL. Min: 3. Max: 6. The default value is [Auto]. DRAM tRCD This controls the number of DRAM clocks for TRCD. Min: 3. Max: 10. The default value is [Auto]. DRAM tRP This controls the number of DRAM clocks for TRP. Min: 3. Max: 10. The default value is [Auto]. DRAM tRAS This controls the number of DRAM clocks for TRAS. Min: 9. Max: 24. The default value is [Auto]. DRAM tRFC This controls the number of DRAM clocks for TRFC. Min: 15. Max: 78. The default value is [Auto]. DRAM tWR This controls the number of DRAM clocks for TWR. Min: 3. Max: 15. The default value is [Auto]. DRAM tRRD This controls the number of DRAM clocks for TRRD. Min: 2. Max: 15. The default value is [Auto]. Rcomp Control G0 Configuration options: [Auto], [1.50X (11)], [1.75X (22)], [2.00X (33)], [2. 25X (44)], [2.50X (55)], [2.75X (66)], [3.00X (77)], [3.25X (88)], [3.50X (99)], [3.75X (AA)], [4.00X (BB)], [4.25X (CC)], [4.50X (DD)], [4.75X (EE)] and [5.00X (FF)]. 31