Brother International MFC-P2000 Service Manual - Page 22

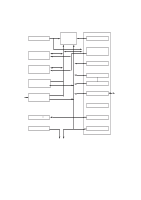

Cdcc / Boise / Data Extension, Bd / Timer 1

|

UPC - 012502525394

View all Brother International MFC-P2000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 22 highlights

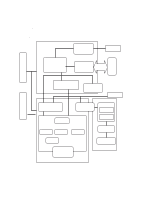

1.3 Main PCB 1.3.1 CPU Core Fig. 2-3 shows the CPU circuit block on the main PCB. The CPU is a Motorola MC68EC000FN16 which is driven at a clock frequency of 15.3 MHz. This clock frequency is made by dividing the source clock of 30.67 MHz by two. Fig. 2-3 1.3.2 ASIC The ASIC is composed of a Cell Based IC that contains the following functional blocks. (1) Oscillator circuit Generates the main clock for the CPU by dividing the source clock frequency by two. (2) Address decoder Generates the CS for each device. (3) DRAM control Generates the RAS, CAS, WE, OE and MA signals for the DRAM and controls refresh processing (CAS before RAS self-refreshing method). (4) Interrupt control Interrupt levels: Priority High 7 6 5 4 3 2 Low 1 NMI FIFO SCANINT BD / Timer 1 SCANINT CDCC / BOISE / DATA EXTENSION Timer 2 II-3