Dell PowerEdge R930 Dell PowerEdge R930 System Owners Manual - Page 4

Active I/O Risers - firmware update

|

View all Dell PowerEdge R930 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 4 highlights

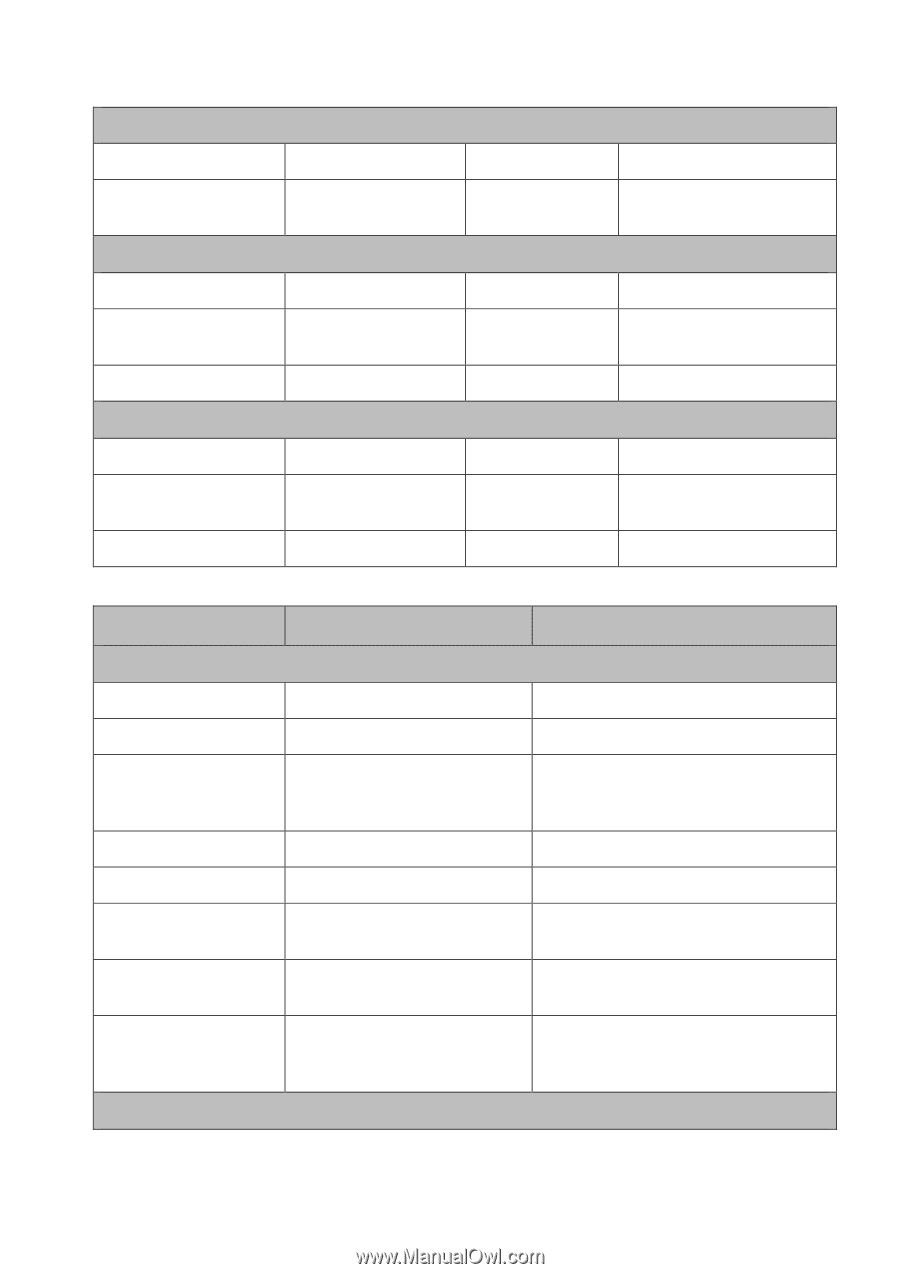

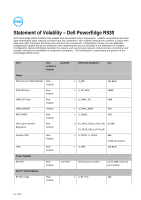

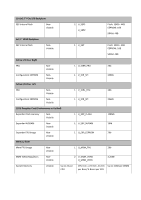

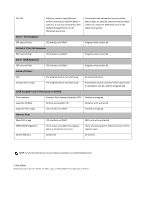

Active I/O Risers I/O Riser FRU image I2C EEPROM No Configuration image EEPROM No 12GB Daughter Card (Performance or Unified) Flash memory Flash No Expander NVRAM NVRAM No Expander FRU image I2C EEPROM No Memory Riser Mem FRU image I2C EEPROM No MEM VDDQ Regulators OTP(one time No programmable) System Memory RAM Yes FRU Firmware that configures PEX switch ports and feature support Firmware Expander Logging Storage during run time FRU FRU Operational parameters System OS RAM Item How is data input to this memory? How is this memory write protected? Planer PBG Internal CMOS NVRAM BIOS N/A - BIOS only control BIOS SPI Flash SPI interface via iDRAC Software write protected iDRAC SPI Flash SPI interface via iDRAC Embedded iDRAC subsystem firmware actively controls sub area based write protection as needed. IDRAC SDRAM Video Interface N/A - Embedded iDRAC video subsystem only BMC EMMC NAND Flash interface via iDRAC Embedded FW write protected CPU Vcore and VSA Regulators Once values are loaded into register space a cmd writes to nvram. There are passwords for different sections of the register space System CPLD OTP(one time programmable) at factory N/A - Factory only control TPM Data is pre-programmed by vendor. Software write protected Keys are updated using TPM-enabled operating systems. Power Supplies