Dell PowerEdge R930 Dell PowerEdge R930 System Owners Manual - Page 5

x2.5 SAS Backplane, 8x2.5 PCIe SSD Backplane, 4x2.5 12GB Backplane, Active I/O Risers, 12GB

|

View all Dell PowerEdge R930 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 5 highlights

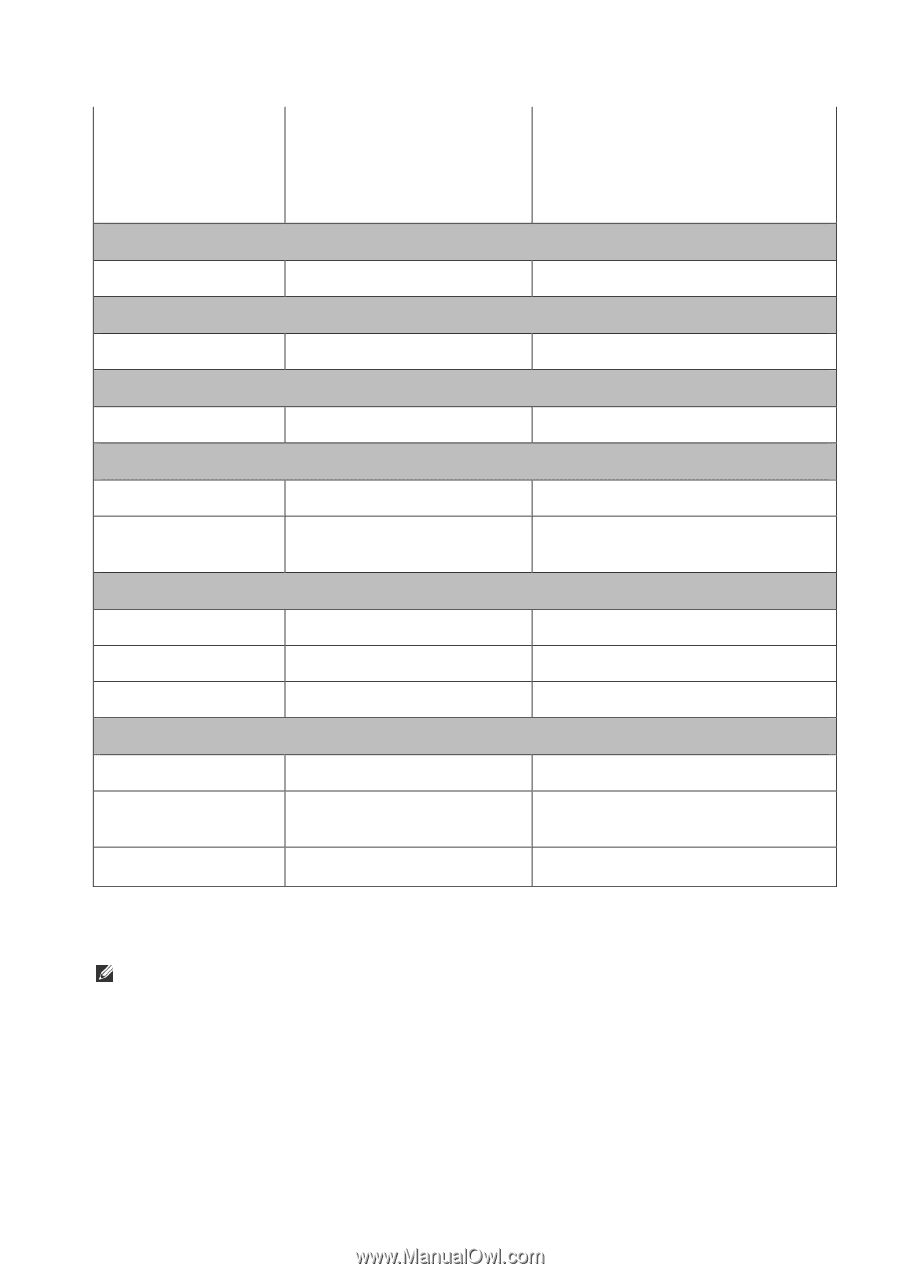

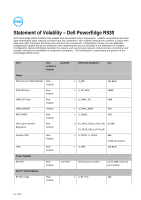

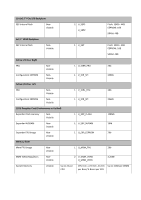

PSU FW Different vendors have different utilities and tools to load the data to memory. It can also be loaded by Dell Update Package from LC or OS (Windows and Linux) Protected by the embedded microcontroller. Special keys are used by special vendor provided utilities to unlock the ROM with various CRC checks during load. 24x2.5" SAS Backplane SEP internal flash I2C interface via iDRAC Program write protect bit 16+8x2.5" PCIe SSD Backplane SEP internal flash I2C interface via iDRAC Program write protect bit 4x2.5" 12GB Backplane SEP internal flash I2C interface via iDRAC Program write protect bit Active I/O Risers FRU Pre-programmed at manufacturing No write protection Configuration image Pre-programmed at manufacturing Protected by switch controller which special tool or application can be used for programming 12GB Daughter Card (Performance or Unified) Flash memory Common Flash memory Interface (CFI) Hardware strapping Expander NVRAM Written by Expander FW Software write protected Expander FRU image I2C interface via iDRAC Hardware strapping Memory Riser Mem FRU image I2C interface via iDRAC FRU is not write protected MEM VDDQ Regulators Once values are loaded into register space a cmd writes to nvram. There are passwords for different sections of the register space System Memory System OS OS Control NOTE: For any information that you may need, direct your questions to your Dell Marketing contact. © 2015 Dell Inc. Trademarks used in this text: Dell™, the DELL logo, and PowerEdge™ are trademarks of Dell Inc.