Foxconn A7GMP-S English Manual. - Page 39

► DRAM Timing Mode, ► CAS Latency - tCL, ► tRCD RAS-to-CAS Delay, ► tRP Precharge Command Period, ►

|

View all Foxconn A7GMP-S manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 39 highlights

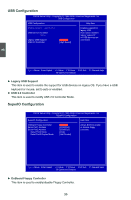

Unganged channels : ■ DCT channels A and B operate as two completely independent 64-bit channels (both chan- nels operate at the same frequency). ■ Reduce DRAM page conflicts - more concurrent open dram pages . ■ Better bus efficiency. Burst lengths supported When both DCTs are enabled in unganged mode, BIOS must initialize the frequency of each DCT in order. DRAM Timing Configuration CMOS Setup Utility - Copyright (C) 1985-2006, American Megatrends, Inc. DRAM Timing Configuration DRAM Timing Configuration Help Item DRAM Timing Mode [Auto] Options Auto = Ganged mode Always = Unganged mode 3 Move Enter:Select +/-/:Value F10:Save ESC:Exit F1:General Help F9:Optimized Defaults ► DRAM Timing Mode When both DCTs (DRAM controller) are enabled in unganged mode, BIOS must initialize the frequency of each DCT in order. Settings are : [Auto]; [DCT 0]. (appear in AM2 CPU) Settings are : [Auto]; [DCT 0]; [DCT1]; [Both]. (appear in AM2+ CPU) ► CAS Latency - tCL The number of memory clocks it takes a DRAM to return data after the read CAS_L is asserted depends on the memory clock frequency. The value that BIOS programs into the memory controller is a function of the target clock frequency. The target clock frequency is determined from the supported CAS latencies at given clock frequencies of each DIMM. ► tRCD (RAS-to-CAS Delay) This item allows you to select a delay time (in clock cycles) between the CAS# and RAS# strobe signals. ► tRP (Precharge Command Period) This item allows you to select the row precharge time (in clock cycles). ► tRTP (Internal Read to Precharge Command Delay) This time allows you to set the delay time (in clock cycles) between read command and pre- 32