LG B2050 Service Manual - Page 39

Display and Interface - specs

|

View all LG B2050 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 39 highlights

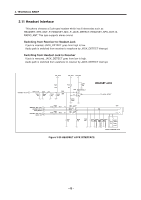

3. TECHNICAL BRIEF 3.7 Display and Interface LCD Properties Active Screen Size Color Depth Resolution Pixel Size Spec. 28.022(H) X 28.022(V) 65,000 128 X RGB X 128 0.063(H) X 0.209(V) Unit mm colors dots mm 10M VSIM V8 VDDUSB VDDRTC A8 _WR _LBS _UBS _RD _ADV _WAIT BURSTCLK TP112 TP114 TP116 28 _MIDI_CS _LCD_CS C129 CLKON 1000p TP122 C130 NA PWRON _RESET RADIO_STO RADIO_DETECT SPK_RADIO_SEL RADIO_SEL LCD_DIM_CTRL RADIO_SDA ONNOFF RADIO_SCL 2 PWRON 1 _F_WP DSR _MIDI_RESET HOOK_DETECT RADIO_VOL_CLK _LCD_RESET LCD_ID SPK_SEL DEBUG_RX DEBUG_TX RADIO_AMP_SHDN C14S02050 _MIDI_IRQ BATT_EPROM RINGTONE M JACK_DETECT RADIO_VOL_CTRL R117 4.7K R118 10K AMP_EN LCD_BL_EN V1 U1 P5 T4 V2 V4 T5 V6 N9 V7 N10 P13 C9 E9 F9 V3 L18 L14 K16 K18 K14 J16 J18 H16 J14 H18 G16 J13 G18 H14 G14 F16 F18 E18 E16 C18 B18 A18 C16 A17 C15 K5 T7 T8 E11 A12 G13 D18 D15 NWE NLWR NHWR NRD NADV NWAIT BURSTCLK NGPCS1 NAUXCS1 GPIO_42_NMAIN_LCD_CS GPIO_43_NSUB_LCD_CS CLKIN CLKON OSCOUT OSCIN PWRON NRESET GPIO_0_IRDA_TX GPIO_1_IRDA_RX GPIO_2_NIRDA_EN GPIO_3 GPIO_4 GPIO_5 GPIO_6 GPIO_7 GPIO_8 GPIO_9 GPIO_10 GPIO_11 GPIO_12 GPIO_13 GPIO_14 GPIO_15 GPIO_16 GPIO_17 GPIO_33_DEBUG_RX GPIO_34_DEBUG_TX GPIO_35 GPIO_36 GPIO_37 GPIO_38 GPIO_39 GPIO_40 GPIO_45 GPIO_46 GPIO_55 GPIO_56 GPO_22_KEY_BACKLIGHT GPO_23_LCD_BACKLIGHT DATA0 L3 L6 DATA1 DATA2 DATA3 L1 L8 DATA4 M1 L5 DATA5 DATA6 N3 DATA7 N1 P3 DATA8 DATA9 N6 DATA10 P1 R3 DATA11 DATA12 R1 DATA13 N7 P6 DATA14 DATA15 T1 TP100 DATA00 DATA01 DATA02 DATA03 DATA04 DATA05 DATA06 DATA07 DATA08 DATA09 DATA10 DATA11 DATA12 DATA13 DATA14 DATA15 Controlled by _LCD_CS, LCD_RESET, _WR, DATA[00:15], LCD_ID, •_LCD_CS : MAIN LCD driver chip enable. MAIN LCD driver IC has own CS pin •LCD_RESET : This pin resets LCD module. This signal comes from DBB directly. •_WR : Write control Signal •_DATA[00:15] : Parallel data lines. •LCD_ID[1:2] : LCD type selection signals -LCD_ID1 : LCD maker (2.4V is SII, 0V is HyeLCD) -LCD_ID[2:3] : for the future using •Forusing 65K color, data buses should be 16 bits. - 38 -