MSI P35 User Guide - Page 60

MS-7345 Mainboard, Configuration DRAM Timing by SPD, DRAM CAS# Latency, DRAM RAS# Precharge, DRAM

|

View all MSI P35 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 60 highlights

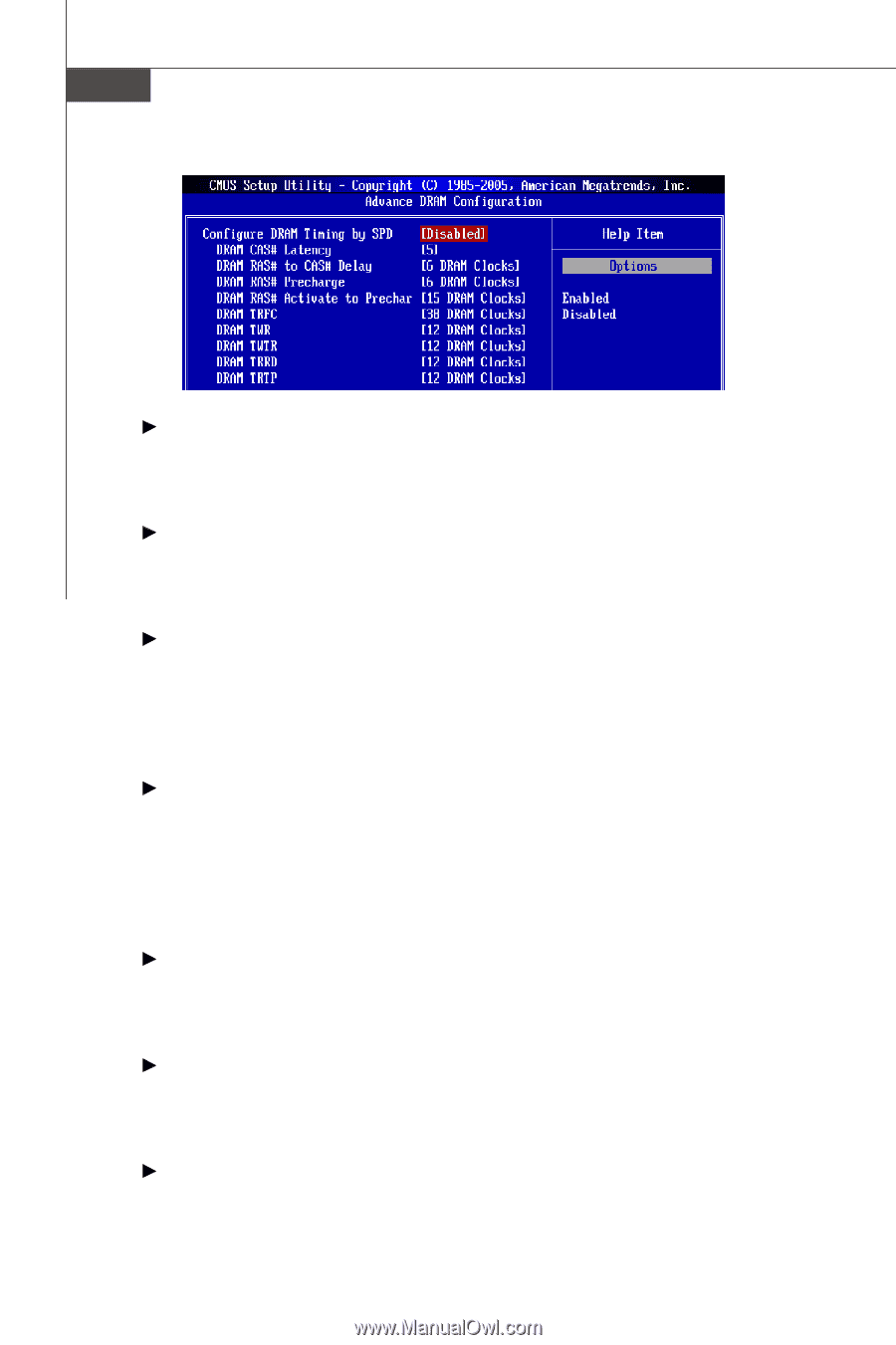

MS-7345 Mainboard Configuration DRAM Timing by SPD Setting to [Enabled] enables DRAM CAS# Latency automatically to be determined by BIOS based on the configurations on the SPD (Serial Presence Detect) EEPROM on the DRAM module. DRAM CAS# Latency W hen the Configuration DRAM Timing by SPD sets to [Disabled], the field is adjustable.This controls the CAS latency, which determines the timing delay (in clock cycles) before SDRAM starts a read command after receiving it. DRAM RAS# to CAS# Delay W hen the Configuration DRAM Timing by SPD sets to [Disabled], the field is adjustable. W hen DRAM is refreshed, both rows and columns are addressed separately. This setup item allows you to determine the timing of the transition from RAS (row address strobe) to CAS (column address strobe). The less the clock cycles, the faster the DRAM performance. DRAM RAS# Precharge W hen the Configuration DRAM Timing by SPD sets to [Disabled], this field is adjustable. This setting controls the number of cycles for Row Address Strobe (RAS) to be allowed to precharge. If insufficient time is allowed for the RAS to accumulate its charge before DRAM refresh, refresh may be incomplete and DRAM may fail to retain data. This item applies only when synchronous DRAM is installed in the system. DRAM TRFC W hen the Configuration DRAM Timing by SPD sets to [Disabled], the field is adjustable. This setting determines the time RFC takes to read from and write to a memory cell. DRAM TWR W hen the Configuration DRAM Timing by SPD sets to [Disabled], the field is adjustable. Minimum time interval between end of write data burst and the start of a precharge command. Allows sense amplifiers to restore data to cells. DRAM TWTR W hen the Configuration DRAM Timing by SPD sets to [Disabled], the field is adjustable. Minimum time interval between the end of write data burst and the 3-22