Pioneer DV-606D Service Manual - Page 17

Ic Information

|

View all Pioneer DV-606D manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 17 highlights

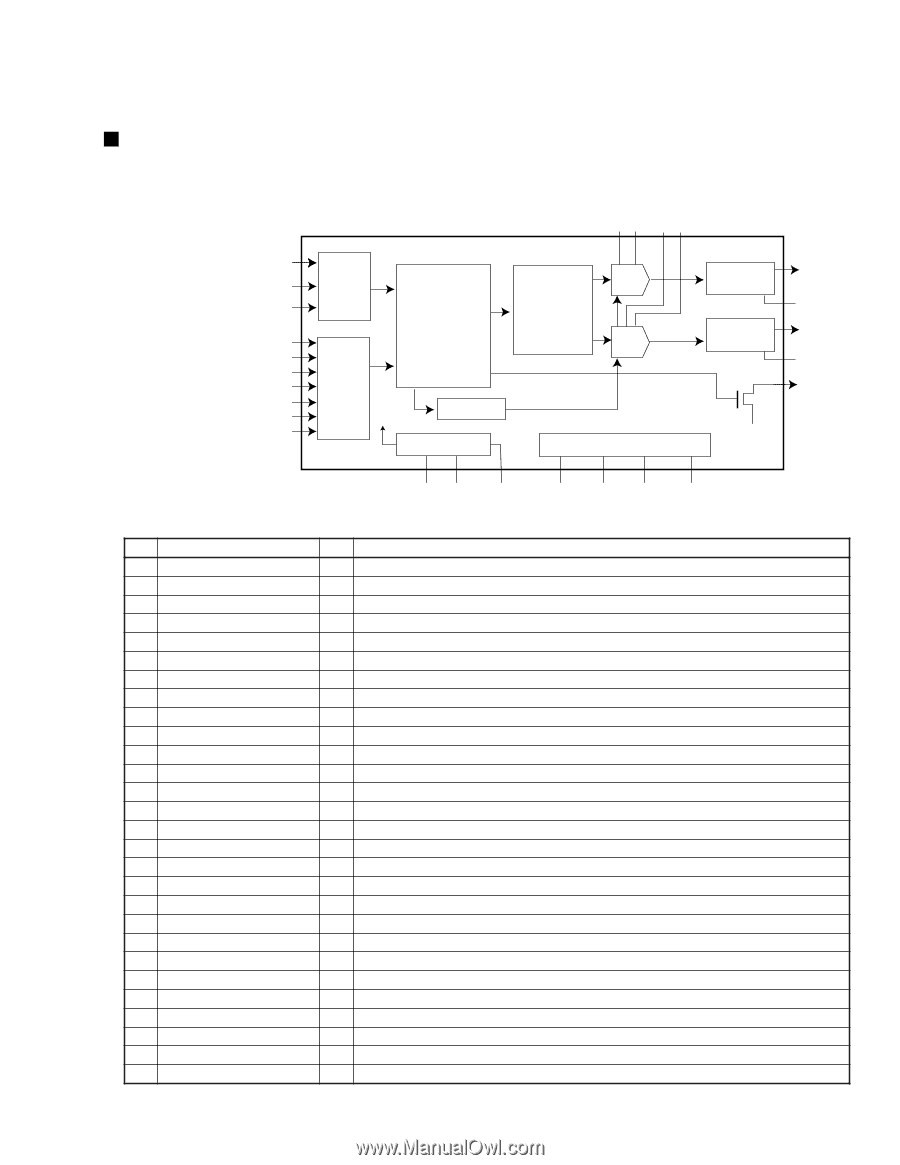

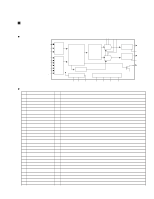

DV-606D 5. IC INFORMATION • The information shown in the list is basic information and may not correspond exactly to that shown in the schematic diagrams. PCM1716E (AVJB ASSY : IC201,IC301 and IC401) • DAC VCC2L AGND2L VCC2R AGND2R ÷ Block Diagram BCKIN LRCIN DIN ML/IIS MC/DM1 MD/DM0 CS/IWO MODE MUTE RST Serial Input 8X I / F Oversampling Digital Filter with Function Mode Controller Control I / F SCK BPZ-Cont. Multi-Level Delta-Signal Modulator DAC DAC Low-pass Filter Low-pass Filter Open Drain Crystal OSC Power Supply VOUTL EXTL VOUTR EXTR ZERO XTI XTO CLKO VCC1 AGND1 VDD DGND ÷ Pin Function No. Pin Name I/O Function 1 LRCIN IN Left & right Clock Input. This clock is equal tothe sampling rate-fs. *1 2 DIN IN Serial Audio DATA Input 3 BCKIN IN Bit Clock Input for Serial Audio DATA 4 CLKO OUT Buffered Output of Oscillator. Equivalent to System Clock. 5 XT1 IN Oscillator Input (External Clock Input) 6 XTO OUT Oscillator Output 7 DGND - Digital Grand 8 VDD - Digital Power +5V 9 VCC2R - Analog Power +5V 10 AGND2R - Analog Grand 11 EXTR OUT R-ch, Common Pin of Analog Output Amp 12 NC - Non Connection 13 VOUTR OUT R-ch Analog Voltage Output of Audio Signal 14 AGND1 - Analog Grand 15 VCC1 - Analog Power +5V 16 VOUTL OUT L-ch Analog Voltage Output of Audio Signal 17 NC - Non Connection 18 EXTL OUT L-ch, Common Pin of Analog Output Amp 19 AGND2L - Analog Grand 20 VCC2L - Analog Power +5V 21 ZERO OUT Zero Data Flag 22 RESET IN Reset. When this pin is low,the DF & Modulator are held in reset. *2 23 CS/IWO IN Chip Select/Input Format Selection. When this pin is low, the Mode Control is effective. *3 24 MODE IN Mode Control Select (H:Software, L:Hardware) *2 25 MUTE IN Mute Control *2 26 MD/DM0 IN Mode Control, Data/De-emphasis selection 1 *2 27 MC/DM1 IN Mode Control, BCK/De-emphasis selection 1 *2 28 ML/IIS IN Mode Control, WDCK/Input format selection 1 *2 *1 : Schmit Trigger input *2 : Schmit Trigger input with pull-up resister *3 : Schmit Trigger input with pull-down resister 17