PlayStation SCPH-7501 Service Manual - Page 7

Reproduction Prohibited - mods

|

View all PlayStation SCPH-7501 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 7 highlights

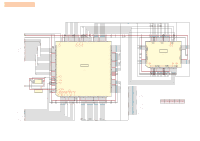

Reproduction Prohibited SCPH-9000 SERIES CONTROLLER SERIAL I/O PU-23 BOARD 102-10 102-8 102-6 102-5 102-3 102-2 102-1 104-1 104-3 104-4 104-5 104-6 104-8 SCK0 TXD RXD DTR0A DTR0B DSR INT RXD DSR TXD CTS DTR RTS Q106 (1/2) Q106 (1/2) Q105 (1/2) Q105 (1/2) 81 SCK0 83 TXD0 84 RXD0 80 DTR0A 77 DTR0B 82 DSR0 89 INTIN10 SIO 75 RXD1 73 DSR1 74 TXD 71 CTS1 72 DTR1 70 RTS1 X201 3, 4 REF. OSC 14.318182MHz (NTSC) 17.37MHz (PAL) IC204 PLL 1 PLL 2 PLL 3 EP ROM CONFIGURABLE MULTIPLEXER AND DIVIDE LOGIC 5 67MHz 4 53.63MHz (NTSC) 1 53.20MHz (PAL) 3.58MHz (NTSC) 6 4.43MHz (PAL) CRYSTALP +8V +5V REG. +3.5V REG. +5V SER +3.5V F001 FULL WAVE RECT. UC 2A/125V AUS/UK/AEP 1.6A/250V DC-AC CONV. SWITCHING REG. POWER SUPPLY BLOCK RECT. RECT. RECT. IC103 CPU GTE CPU CORE MDEC +8V +3.5V SYSTEM RESET VD0-VD31 161-165, 172-181, 184-194, 197, 198 MAIN DATA BUS (GPUD0-GPUD31) SD0-SD15 107-116, 119-142 SUB DATA BUS (SD0-SD15) SA0-SA23 145-152, 132-142, 125-129 ADDRESS BUS (SA0-SA23) B/U 97 CS2 SRD 23, 25-31 1-12 IC102 13-15, 17-21 24 A0-A19 D0-D7 OE 22 BOOT RAM CE DRAM CONTROLLER DD0-DD31 DA0-DA7 DA9 DA11 DWE DRAS0 5-13, 16-25, 28-37, 40-42 55, 57, 59-64 67, 68 43 45 2-5, 7-10,13-16,18-21 50-53,55-58,61-64,66-69 IC106 HYPER DRAM (16M) I/O1-I/O32 28-34, 37-39 A0-A9 IC106 44 WE 27 RAS CAS1-4 45-48 46-49 4 DCAS0-DCAS3 OE RES3.3 102 INT IN1 153 VA2 159 TCLK1 160 TCCK0 199 INT IN0 200 DREQ2 201 SYSCLK0 202 DACK2 203 VWR 204 VRD 205 CS7 206 DSYSCLK DREQ4 88 INT IN9 90 DACK4 87 CS4 96 101 SRD 100 SWR0 154 SYSCLK1 95 CS5 94 INT IN2 GPUNIT GPUA2 H BLANK PCK V BLANK GPUDREQ SYSCLK0 GPUDACK GPUWR GPURD GPUCS DBLCLK SPUDREQ SPUNIT SPUDACK SPUCS SRD SWR0 SYSCLK1 IC304 49 LDON 28 MIRROR SUB CPU LDON AGC_CNT SPUDREQ SPUNIT SPUDACK SRD SWR0 SPUCS SYSCLK1 EXTDATA 36 DREQ 35 XIRQ 34 DACK 32 XRD 33 XWR 31 XCS 41 SYSCLK1 96 DTIB S301 19 DOOR 33-38, 40, 41 DECD0-DECD7 MCD0-MCD7 6-10 DECA0-DECA4 MCA0-MCA4 27 SPEED 43 DATA 44 XLT 45 CLK 31 SCOR 26 SQCK 24 SUB Q 18 LMTSW 14 DSC1 13 RESET 46 DECCS 47 DECWR 48 DECRD 30 X INT 23 SENSE SPEED DAT0 XLT0 CLK0 SCOR SQCK SUB Q LS MCLK XRST MCS MWR MRD MINT SENS CD RD CS CD RD INT RES3.3 6 24-28, 31-36, 39-42, 45-50, 53-59, 62-65 RST D0-D31 GPUNIT GPUA2 H BLANK PCK V BLANK GPUDREQ SYSCLK0 GPUDACK GPUWR GPURD GPUCS DBLCLK 13 IREQ 2 A2 14 H BLANK 199 PCK 17 V BLANK 12 DREQ 9 SYSCLK 5 DACK 4 WR 3 RD 1 CS 206 D SYSCK 192 VCKN-A FD0-FD31 IC203 GPU LA0-LA9 SR0-SR7 R R DECODER LATCH SG0-SG7 G G DECODER LATCH SB0-SB7 B B DECODER LATCH 156 C SYNC 157 NTPL 14 SYNC IN 15 SC IN 13 NT/PAL IC502 VIDEO DAC + RGB ENCODER CELL MATRIX CELL MATRIX CELL MATRIX CLAMP CLAMP CLAMP R G B MATRIX Y B-Y R-Y SYNC ADD CHROMA GEN. BURST FLAG 6dB 75 6dB 75 6dB 75 6dB 75 LPF 75 BPF Y TRAP Y/C M/X 75 127 DQMH 128 DQML 126 WE 125 CAS 124 RAS 122 MCS0 123 DSF 131 MCLKOUT 134 MCLKIN 77-79, 82-86 89-95, 98-104 107-112, 115-118 1, 3, 4, 6, 7, 9, 10, 12, 13, 17, 18, 20, 21, 60, 61, 63, 64, 68, 69, 71, 72, 74, 75, 77, 78, 80, 81, 83, 84 137-140 143-145 148-150 29, 31-34 47-51 DQ0-DQ31 A0-A9 IC201 SPMUTE 5 AU-R 7 AU-L 11 SERIAL INPUT INTERFACE IC405 8x INTERPOLATOR ∆∑ MODULATOR SCF 56 DQM1 57 DQM3 23 DQM0 24 DQM2 25 WE 26 CAS 27 RAS 28 CS 53 DSF 55 CLK SG RAM 8x INTERPOLATOR ∆∑ MODULATOR SCF 1, 2, 5-14 16-19 SD0-SD15 20-27, 30 SA1-SA9 FROM IC103 SPUDREQ SRD SWR0 SPUDACK SYSCLK1 HD0-HD15 HOST HA1-HA8 IF DMA TIMING GEN ENV DTIB BCK0 LRC0 SERIAL IF DSP SERIAL INPUT INTERFACE 8x INTERPOLATOR 8x INTERPOLATOR IC732 MD0-MD15 160-164, 166-172 174-177 MED0-MED15 EXRAM IF MA1-MA9 183-186, 188-192 MEA0-MEA8 XOE 181 XWE 179 XRAS 182 XCAS 178 MUTO 154 ∆∑ MOD SCF AOUTL 147 ∆∑ MOD SCF AOUTR 150 XLT1 105 RESET 4 SPMUTE 5 CLOCK DIVIDER 6 7 SPCLK 2-5, 7-10 31-34, 36-39 IC310 I/O 1-16 15 16-19, 22-26 A0-A8 13 4Mbit DRAM 11 27 OE 13 12 WE 14 RAS 16 28 UCAS 29 LCAS 19 18 VREFL +5V IC723 CD-RF AMP AMP AMP AMP AMP AMP APC 9 125-142 SD0-SD15 HD0-HD15 105,107-111,113-116 SA0-SA9 HA0-HA9 A/D CONVERTER 27 37 38 SWITCH 39 AND BUFFER 85-92 MCD0-MCD7 97-99,101,102 MCA0-MCA4 SUB CPU I/F 74 DATA 75 XLAT 76 CLOK 77 SCOR 80 SQCK 81 SQS0 11 FSOF MIRR DFCT FOK SERVO DSP TRACKING 57 PWM 55 GENERATOR PWM GENERATOR TRACKING PWM GENERATOR 53 54 TRACKING 58 PWM 59 GENERATOR SYNC TIMING CLV 122 PROTECTOR GENERATOR PROTECTOR 94 XCS 95 XWR 96 XRD 79 XINT 82 SENS 103 XHCS 117 H INT CD-ROM CONTROLLER + CD DSP 119 XHRD 120 XHWR 144 SYSCK RFAC FE SE TFDR TRDR FRDR FFDR SRDR SFDR SRD SWR0 FROM IC103 SYSCLK1 IC722 DRIVER 11 6 BUFF 7 LEVEL AMP SHIFT 12 BUFF 13 5 BUFF 4 AMP LEVEL SHIFT 14 BUFF 17 22 BUFF 23 AMP LEVEL SHIFT 18 BUFF 15 2 LEVEL BUFF AMP SHIFT 16 BUFF 3 SPEED 20 RESET M_R M_G M_B M_Y 502-2 502-1 502-4 502-8 M_C 502-6 M_VIDEO 502-7 AV MULTI OUT VOOM 12 TRM_L 13 M_AUL 502-11 TRM_R 2 M_AUR 502-9 7 6 5 4 8 Q701 +B REG 702-7 702-6 702-8 702-4 MI 702-9 LD 702-1 702-10 KSM440AEM PD1 PD2 PDIC E F LASER DIODE 702-15 702-14 702-16 702-13 701-1 701-2 701-4 701-3 TRK- TRK+ FCS- FCS+ SL- SL+ SP- SP+ TRACKING COIL FOCUS COIL M SLED MOTOR SPINDLE MOTOR BLOCK RES3.3 LD 702-12 - 6 -