TEAC DW-224E-V Hardware Specification - Page 17

Fig. 14.4-1, Reset timing master, Fig. 14.4-2, Reset timing slave

|

View all TEAC DW-224E-V manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 17 highlights

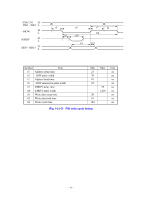

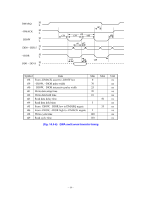

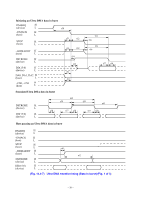

-RESET H L t1 -DASP H L -PDIAG H L Symbol Item t1 -HRST pulse width Min Typ Max Unit 25 µs (Fig. 14.4-1) Reset timing (master) -RESET H L -DASP H L -PDIAG H L t2 t4 Symbol Item t2 -DASP assert time t4 -PDIAG assert start Min Typ Max Unit 70 400 ms 0.2 30 s (Fig. 14.4-2) Reset timing (slave) - 15 -

° 15 °

(Fig. 14.4-1)

Reset timing (master)

(Fig. 14.4-2)

Reset timing (slave)

Symbol

Item

Min

Typ

Max

Unit

t1

°HRST pulse width

25

µ

s

Symbol

Item

Min

Typ

Max

Unit

t2

°DASP assert time

70

400

ms

t4

°PDIAG assert start

0.2

30

s

H

L

°RESET

H

L

H

L

°DASP

°PDIAG

t1

H

L

°RESET

H

L

H

L

°DASP

°PDIAG

t2

t4