Foxconn G41MD-V English Manual - Page 40

► North Bridge Configuration/ South Bridge Configuration, ► Memory Remap Feature, ► DRAM Frequency, ►

|

View all Foxconn G41MD-V manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 40 highlights

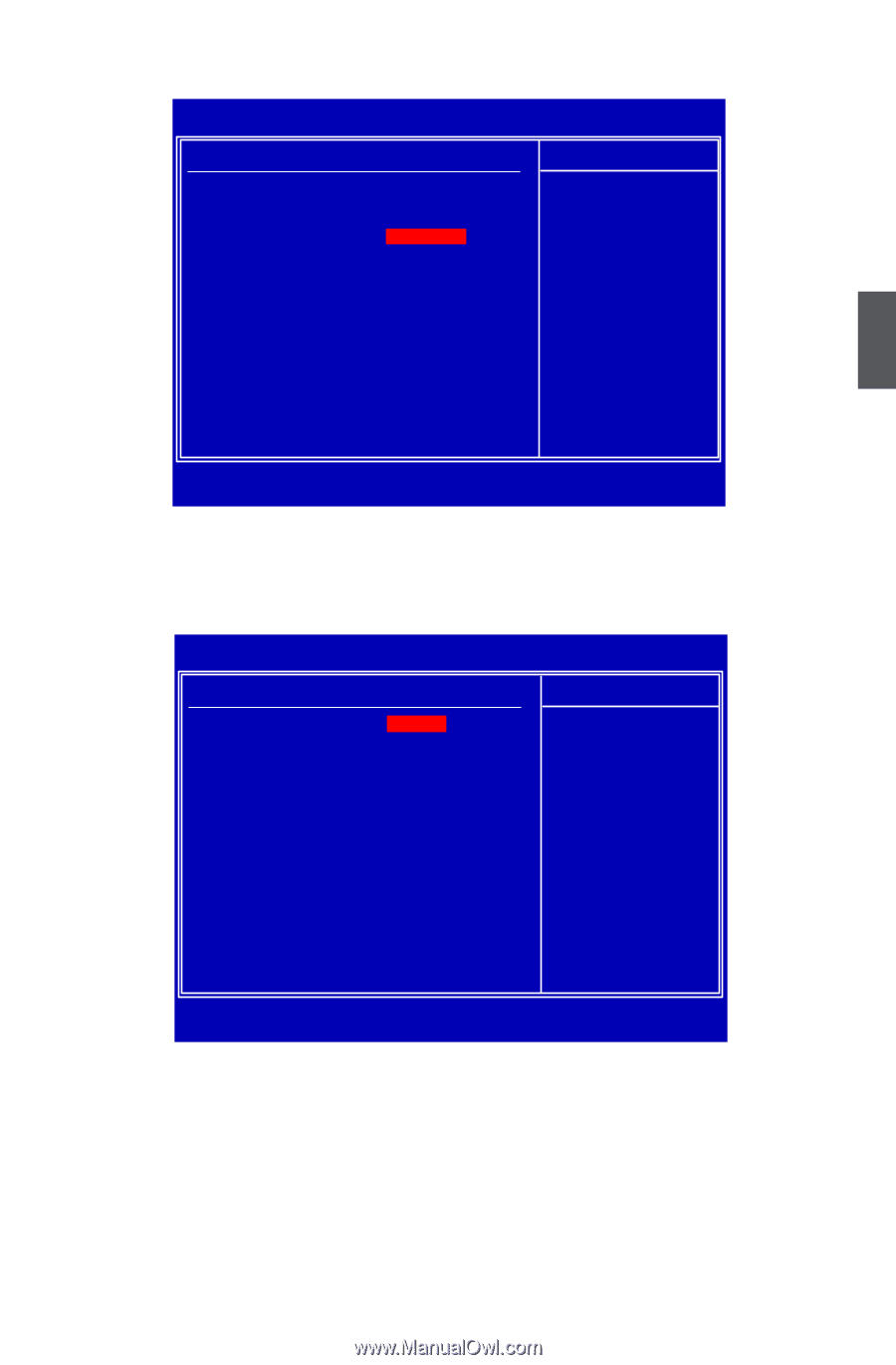

Advanced Chipset Features CMOS Setup Utility - Copyright (C) 1985-2008, American Megatrends, Inc. Advanced Chipset Features Advanced Chipset Settings Help Item WARNING: Setting wrong values in below sections Configure North Bridge may cause system to malfunction. features. N��o�rt�h��B�r�id��g�e��C�o�n��fi�g�u�r�a�t�io�n� [Press Enter] S�o��u�th��B�r�i�d�g�e��C�o��n�fi�g�u�r�a�t�io�n� [Press Enter] 3 Move Enter:Select +/-/:Value F10:Save ESC:Exit F1:General Help F9:Optimized Defaults ► North Bridge Configuration/ South Bridge Configuration Press to go to its submenu. North Bridge Configuration CMOS Setup Utility - Copyright (C) 1985-2008, American Megatrends, Inc. North Bridge Configuration �N��o�r�th��B��ri�d�g�e��C��h�i�p�s�e�t�C��o�n�f�i�g�u�r�a�t�io�n� Help Item Memory Remap Feature [Enabled] ENABLE: Allow PCI MMIO Allocation:4GB To 3328MB remapping of DRAM Frequency Au�to ov�e�rla�p�pe�d�P�C�I m�e�m�o�ry �M�e�m�o�ry�C�o�m�m�a�n�d�R�a�te A��u��t�o a�b��o�v�e���th��e��t�o�t�al Memory Timing by SPD E�n�ab�le�d ph�y�si�ca�l �m�em�o�r�y. Memory Hole [Disabled] Initate Graphic Adapter P�E�G�/P�C�I D�I�S�A�BL�E�:�D�o�n�o�t a�ll�o�w IGD GTT Graphic smemory size [No VT mode, 2MB] remapping of memory. DVMT Mode Select D�VM�T�M�o�d�e] PEG Port [Auto] Move Enter:Select +/-/:Value F10:Save ESC:Exit F1:General Help F9:Optimized Defaults ► Memory Remap Feature This item is used to enable/disable memory remap feature. Its mainly for if you have a 64bit OS and 4GB of RAM. Basically it allows you to remap the overlapped PCI memory above the total physical memory. ► DRAM Frequency This item is used to adjust the DRAM frequency. Select [Auto] for SPD enable mode. You also can select a value manually such as [800 MHz]. ► Memory Command Rate This feature allows you to select the delay between the assertion of the Chip Select signal till 33