Foxconn G41MD-V English Manual - Page 42

► SMBUS Controller, ► SLP_S4# Min. Assertion Width, ► ASPM

|

View all Foxconn G41MD-V manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 42 highlights

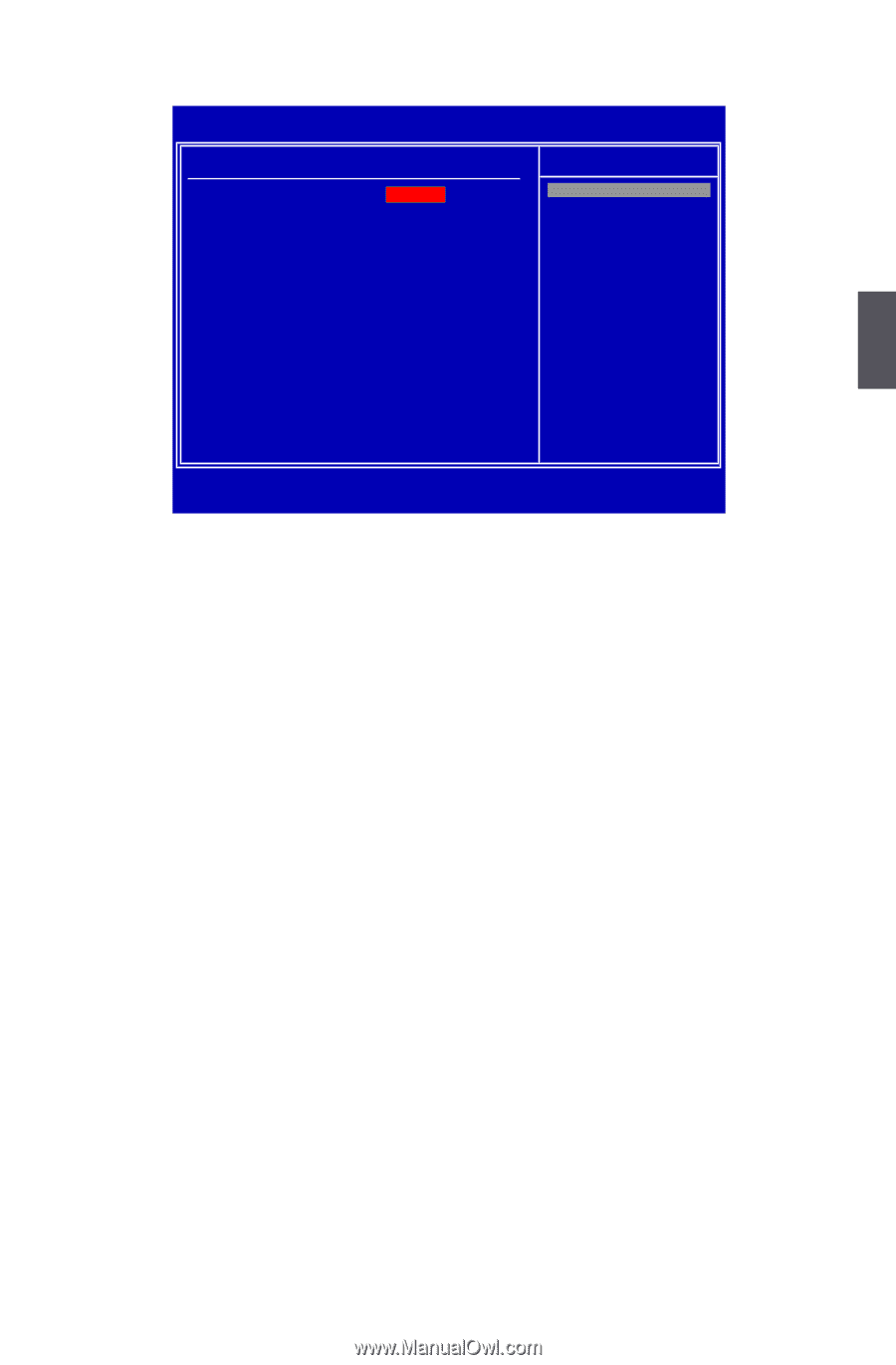

South Bridge Configuration CMOS Setup Utility - Copyright (C) 1985-2008, American Megatrends, Inc. South Bridge Configuration �S��o�u�t�h��B�r�id�g��e�C��h�i�p�s�e�t��C�o�n��fi�g�u�r�a�t�io�n� Help Item �S�M�B�U��S�C�o�n�t�ro�ll�e�r E�n�a�b�le�d Options SLP_S4# Min. Assertion Width [1 to 2 seconds] Enabled Disabled ASPM [�D�i�s�a�b�le��d��] 3 Move Enter:Select +/-/:Value F10:Save ESC:Exit F1:General Help F9:Optimized Defaults ► SMBUS Controller The System Management Bus is a specific implementation of an I2C bus. The SMBus specification describes the data protocols, device addresses, and electrical requirements that are superimposed on the I2C bus specification. The SMBus is used to physically transport commands and information between the Smart Battery, SMBus Host, Smart Battery Charger, and other SMBus Devices. This item is used to enable/disable System Management Bus controller. ► SLP_S4# Min. Assertion Width SLP_S4# is a signal for power plane control. This signal shuts off power to all non-critical systems when in the S4 (Suspend to Disk) or S5 (Soft Off) state. This setting indicates the minimum assertion width of the SLP_S4# signal to ensure that the DRAMs have been safely power-cycled. Setting values are: [4 to 5 seconds], [3 to 4 seconds], [2 to 3 seconds], [1 to 2 seconds]. ► ASPM Active State Power Management (ASPM) allows power to be incrementally reduced to individual serial links in a PCI Express fabric as a link becomes less active. ASPM is defined in the PCI Express base specification. Enables or disables ASPM for a Link, based on the overall system power policy, the hardware capabilities of the Link, and the latency of the Link. Hardware performs the actual power management operations of transitioning Links between Link power states and resynchronizing Links. The configuration of the PCI Express implementation on a system affects the amount of power savings that can actually be achieved. This item is used to enable/disable this feature. 35