Gigabyte GA-G1975X Manual

Gigabyte GA-G1975X Manual

|

View all Gigabyte GA-G1975X manuals

Add to My Manuals

Save this manual to your list of manuals |

Gigabyte GA-G1975X manual content summary:

- Gigabyte GA-G1975X | Manual - Page 1

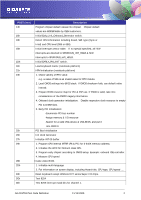

flash type to load appropriate flash R/W codes into the run time area in F000 for ESCD & DMI support. 12h Use walking 1's algorithm to check out interface in CMOS circuitry. Also set real-time clock power status, and then check for override. GA-G1975X Post Code Definition 11/14/2005 1 - Gigabyte GA-G1975X | Manual - Page 2

. 4. Measure CPU speed Invoke video BIOS. 1. Initialize multi-language 2. Put information on screen display, including Award title, CPU type, CPU speed .... Reset keyboard except Winbond 977 series Super I/O chips. Test 8254 Test 8259 interrupt mask bits for channel 1. GA-G1975X Post Code - Gigabyte GA-G1975X | Manual - Page 3

each CPU are not identical. Initialize USB Test all memory (clear all extended memory to 0) Display number of processors (multi-processor platform) 1. Display not until this POST stage can users enter the CMOS setup utility. Initialize PS/2 Mouse Prepare memory size information for function call: - Gigabyte GA-G1975X | Manual - Page 4

co-processor 1. Switch back to text mode if full screen logo is supported. ACPI table at top of memory. 5. Invoke ISA adapter Update keyboard LED & typematic rate 96h 1. Build MP table 2. Build & update ESCD 3. Set CMOS century to 20h or 19h 4. Load CMOS time into DOS timer tick GA-G1975X - Gigabyte GA-G1975X | Manual - Page 5

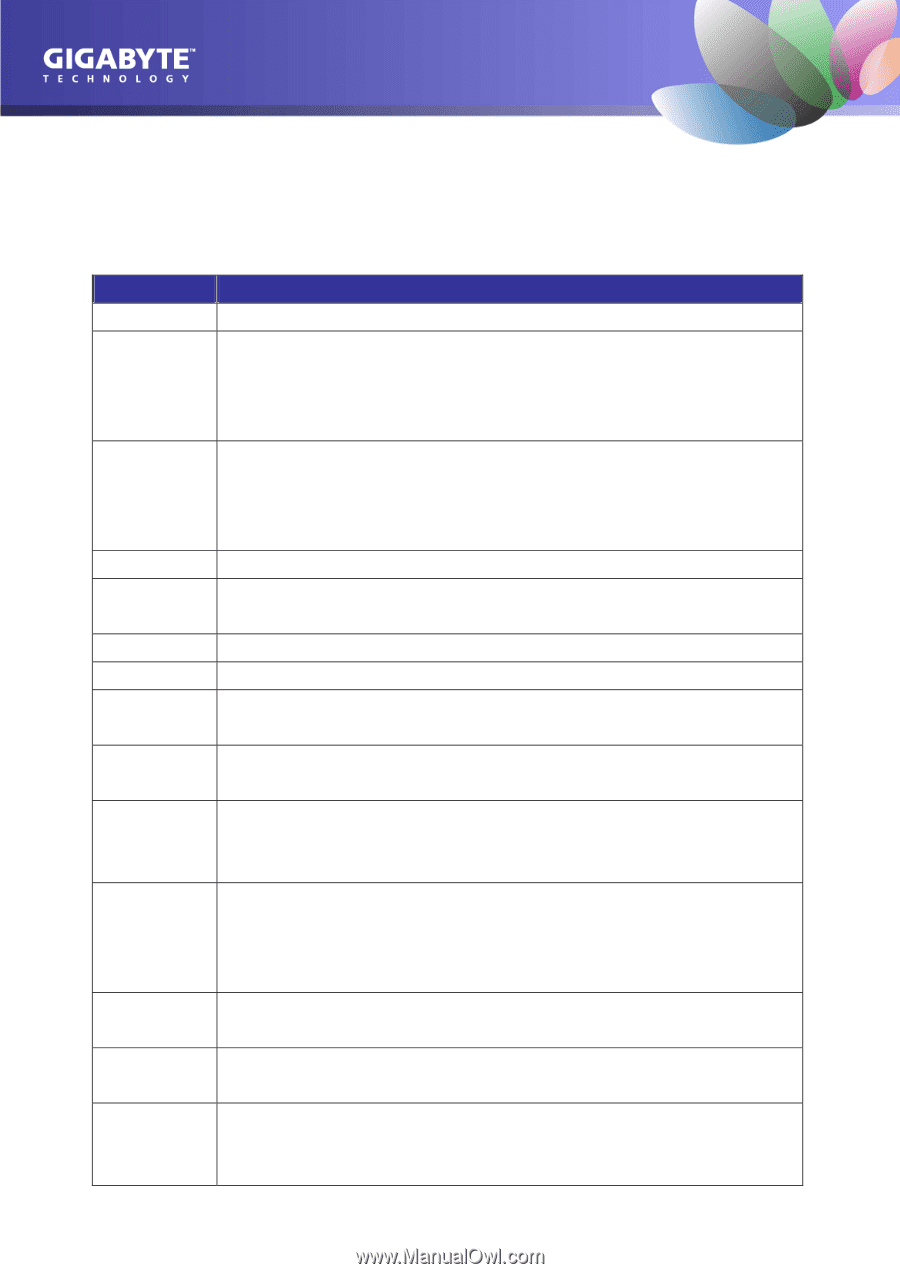

POST (hex) FFh 5. Build MSIRQ routing table. Boot attempt (INT 19h) Description GA-G1975X Post Code Definition 11/14/2005 5

______________________________________________________________________________________________

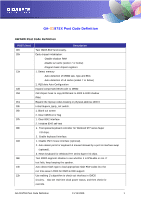

GA-G1975X Post Code Definition

11/14/2005

1

GA-

G1

975X Post Code Definition

AWARD Post Code Definition

POST (hex)

Description

CFh

Test CMOS R/W functionality.

C0h

Early chipset initialization:

-Disable shadow RAM

-Disable L2 cache (socket 7 or below)

-Program basic chipset registers

C1h

1. Detect memory

-Auto-detection of DRAM size, type and ECC.

-Auto-detection of L2 cache (socket 7 or below)

2. PEG slots Auto-Configuration

C3h

Expand compressed BIOS code to DRAM

C5h

Call chipset hook to copy BIOS back to E000 & F000 shadow

RAM.

0h1

Expand the Xgroup codes locating in physical address 1000:0

03h

Initial Superio_Early_Init switch.

05h

1. Blank out screen

2. Clear CMOS error flag

07h

1. Clear 8042 interface

2. Initialize 8042 self-test

08h

1.

Test special keyboard controller for Winbond 977 series Super

I/O chips.

2.

Enable keyboard interface.

0Ah

1.

Disable PS/2 mouse interface (optional).

2.

Auto detect ports for keyboard & mouse followed by a port & interface swap

(optional).

3.

Reset keyboard for Winbond 977 series Super I/O chips.

0Eh

Test F000h segment shadow to see whether it is R/W-able or not. If

test fails, keep beeping the speaker.

10h

Auto detect flash type to load appropriate flash R/W codes into the

run time area in F000 for ESCD & DMI support.

12h

Use walking 1’s algorithm to check out interface in CMOS

circuitry.

Also set real-time clock power status, and then check for

override.