Gigabyte GA-G1975X Manual - Page 2

POST hex, Description - video

|

View all Gigabyte GA-G1975X manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 2 highlights

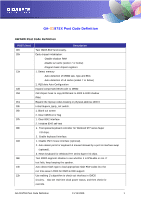

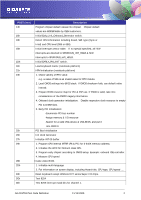

POST (hex) 14h 16h 18h 1Bh 1Dh 1Fh 21h 23h 25h 26h 27h 29h 2Bh 2Dh 33h 3Ch 3Eh Description Program chipset default values into chipset. Chipset default values are MODBINable by OEM customers. Initial Early_Init_Onboard_Generator switch. Detect CPU information including brand, SMI type (Cyrix or Intel) and CPU level (586 or 686). Initial interrupts vector table. If no special specified, all H/W interrupts are directed to SPURIOUS_INT_HDLR & S/W interrupts to SPURIOUS_soft_HDLR. Initial EARLY_PM_INIT switch. Load keyboard matrix (notebook platform) HPM initialization (notebook platform) 1. Check validity of RTC value: e.g. a value of 5Ah is an invalid value for RTC minute. 2. Load CMOS settings into BIOS stack. If CMOS checksum fails, use default value instead. 3. Prepare BIOS resource map for PCI & PnP use. If ESCD is valid, take into consideration of the ESCD's legacy information. 4. Onboard clock generator initialization. Disable respective clock resource to empty PCI & DIMM slots. 5. Early PCI initialization: -Enumerate PCI bus number -Assign memory & I/O resource -Search for a valid VGA device & VGA BIOS, and put it into C000:0. PCI Bus Initialization Init clock Generator Initialize INT 09 buffer 1. Program CPU internal MTRR (P6 & PII) for 0-640K memory address. 2. Initialize the APIC for Pentium class CPU. 3. Program early chipset according to CMOS setup. Example: onboard IDE controller. 4. Measure CPU speed Invoke video BIOS. 1. Initialize multi-language 2. Put information on screen display, including Award title, CPU type, CPU speed .... Reset keyboard except Winbond 977 series Super I/O chips. Test 8254 Test 8259 interrupt mask bits for channel 1. GA-G1975X Post Code Definition 11/14/2005 2