Seagate ST3500630A Serial ATA Native Command Queuing (670K, PDF) - Page 5

Detailed Description of NCQ, Building a Queue - parts

|

UPC - 000067575145

View all Seagate ST3500630A manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 5 highlights

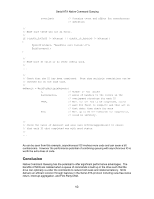

Serial ATA Native Command Queuing Native Command Queuing achieves high performance and efficiency through efficient command re-ordering. In addition, there are three new capabilities that are built into the Serial ATA protocol to enhance NCQ performance including race-free status return, interrupt aggregation, and First Party DMA. • Race-Free Status Return Mechanism This feature allows status to be communicated about any command at any time. There is no "handshake" required with the host for this status return to take place. The drive may issue command completions for multiple commands back-to-back or even at the same time. • Interrupt Aggregation Generally, the drive interrupts the host each time it completes a command. The more interrupts, the bigger the host processing burden. However, with NCQ, the average number of interrupts per command can be less than one. If the drive completes multiple commands in a short time span - a frequent occurrence with a highly queued workload - the individual interrupts may be aggregated. In that case, the host controller only has to process one interrupt for multiple commands. • First Party DMA (FPDMA) Native Command Queuing has a mechanism that lets the drive set up the Direct Memory Access (DMA) operation for a data transfer without host software intervention. This mechanism is called First Party DMA. The drive selects the DMA context by sending a DMA Setup FIS (Frame Information Structure) to the host controller. This FIS specifies the tag of the command for which the DMA is being set up. Based on the tag value, the host controller will load the PRD table pointer for that command into the DMA engine, and the transfer can proceed without any software intervention. This is the means by which the drive can effectively re-order commands since it can select the buffer to transfer on its own initiative. Detailed Description of NCQ There are three main components to Native Command Queuing: 1. Building a queue of commands in the drive 2. Transferring data for each command 3. Returning status for the commands that were completed The following sections will detail how each mechanism works. Building a Queue The drive must know when it receives a particular command whether it should queue the command or whether it should execute that command immediately. In addition, the drive must understand the protocol to use for a received command; the command protocol could be NCQ, DMA, PIO, etc. The drive determines this information by the particular command opcode that is issued. Therefore in order to take advantage of NCQ, commands that are specifically for NCQ were defined. There are two NCQ commands that were added as part of the NCQ definition in Serial ATA II, Read FPDMA Queued and Write FPDMA Queued. The Read FPDMA Queued command inputs are shown in Figure 1; the inputs for Write FPDMA Queued are similar. The commands are extended LBA and sector count commands to accommodate the large capacities in today's drives. 5